Datasheet Texas Instruments TMS320C6472 — Даташит

| Производитель | Texas Instruments |

| Серия | TMS320C6472 |

Fixed-Point Digital Signal Processor

Datasheets

TMS320C6472 Fixed-Point Digital Signal Processor datasheet

PDF, 1.8 Мб, Версия: G, Файл опубликован: 30 июн 2011

Выписка из документа

Цены

Купить TMS320C6472 на РадиоЛоцман.Цены — от 74 до 40 699 ₽ Купить TMS320C6472 на РадиоЛоцман.Цены — от 74 до 40 699 ₽22 предложений от 18 поставщиков Процессоры и контроллеры цифровых сигналов (DSP, DSC) TMS320C647X DSP - FIXED-POINT DIGITAL SIGNAL PROCESSOR | |||

| TMS320C6472EZTZ Texas Instruments | 74 ₽ | ||

| TMS320C6472ECTZ Texas Instruments | 11 797 ₽ | ||

| TMS320C6472ECTZ Texas Instruments | от 32 935 ₽ | ||

| TMS320C6472EZTZ7 Texas Instruments | по запросу | ||

Статус

| TMS320C6472ECTZ | TMS320C6472ECTZ7 | TMS320C6472ECTZA6 | TMS320C6472EZTZ | TMS320C6472EZTZ6 | TMS320C6472EZTZ7 | TMS320C6472EZTZA | TMS320C6472EZTZA6 | |

|---|---|---|---|---|---|---|---|---|

| Статус продукта | В производстве | В производстве | В производстве | Скоро будет снят с производства | Скоро будет снят с производства | Скоро будет снят с производства | Скоро будет снят с производства | Скоро будет снят с производства |

| Доступность образцов у производителя | Нет | Нет | Нет | Нет | Нет | Нет | Нет | Нет |

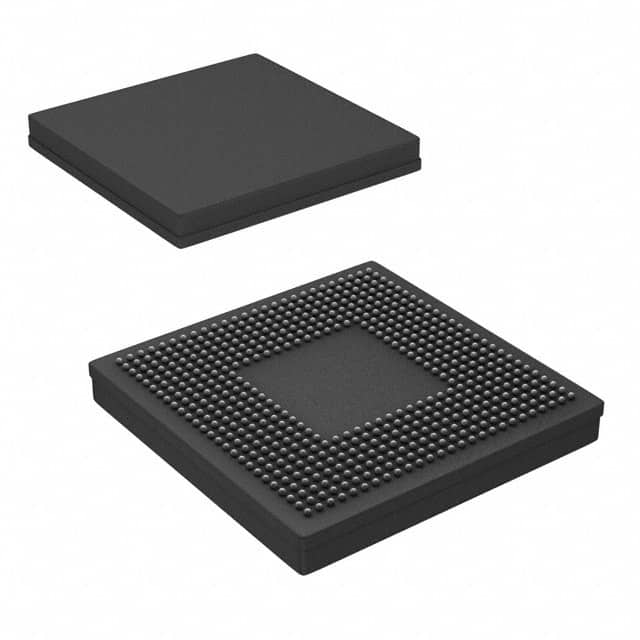

Корпус / Упаковка / Маркировка

| TMS320C6472ECTZ | TMS320C6472ECTZ7 | TMS320C6472ECTZA6 | TMS320C6472EZTZ | TMS320C6472EZTZ6 | TMS320C6472EZTZ7 | TMS320C6472EZTZA | TMS320C6472EZTZA6 | |

|---|---|---|---|---|---|---|---|---|

| N | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Pin | 737 | 737 | 737 | 737 | 737 | 737 | 737 | 737 |

| Package Type | CTZ | CTZ | CTZ | ZTZ | ZTZ | ZTZ | ZTZ | ZTZ |

| Package QTY | 44 | 44 | 44 | |||||

| Carrier | JEDEC TRAY (5+1) | JEDEC TRAY (5+1) | JEDEC TRAY (5+1) | |||||

| Маркировка | @2007 TI | TMS320C6472CTZ | TMS320C6472CTZA | TMS320C6472 | 625 | TMS320C6472 | TMS320C6472 | 625 |

| Width (мм) | 24 | 24 | 24 | 24 | 24 | 24 | 24 | 24 |

| Length (мм) | 24 | 24 | 24 | 24 | 24 | 24 | 24 | 24 |

| Thickness (мм) | 2.65 | 2.65 | 2.65 | 2.65 | 2.65 | 2.65 | 2.65 | 2.65 |

| Mechanical Data | Скачать | Скачать | Скачать | Скачать | Скачать | Скачать | Скачать | Скачать |

| Industry STD Term | FCBGA | FCBGA | FCBGA | FCBGA | FCBGA | |||

| JEDEC Code | S-PBGA-N | S-PBGA-N | S-PBGA-N | S-PBGA-N | S-PBGA-N | |||

| Pitch (мм) | .8 | .8 | .8 | .8 | .8 | |||

| Max Height (мм) | 3.5 | 3.5 | 3.5 | 3.5 | 3.5 |

Параметры

| Parameters / Models | TMS320C6472ECTZ | TMS320C6472ECTZ7 | TMS320C6472ECTZA6 | TMS320C6472EZTZ | TMS320C6472EZTZ6 | TMS320C6472EZTZ7 | TMS320C6472EZTZA | TMS320C6472EZTZA6 |

|---|---|---|---|---|---|---|---|---|

| Approx. Price (US$) | 142.80 | 1ku | 142.80 | 1ku | 142.80 | 1ku | 142.80 | 1ku | 142.80 | 1ku | |||

| DSP | 6 C64x+ | 6 C64x+ | 6 C64x+ | 6 C64x+ | 6 C64x+ | 6 C64x+ | 6 C64x+ | 6 C64x+ |

| Rating | Catalog | Catalog | Catalog | Catalog | Catalog | Catalog | Catalog | Catalog |

Экологический статус

| TMS320C6472ECTZ | TMS320C6472ECTZ7 | TMS320C6472ECTZA6 | TMS320C6472EZTZ | TMS320C6472EZTZ6 | TMS320C6472EZTZ7 | TMS320C6472EZTZA | TMS320C6472EZTZA6 | |

|---|---|---|---|---|---|---|---|---|

| RoHS | Совместим | Совместим | Совместим | Не совместим | Не совместим | Не совместим | Не совместим | Не совместим |

| Бессвинцовая технология (Pb Free) | Нет | Нет | Нет | Нет | Нет |

Application Notes

- TMS320C6472/TMS320TCI6486 DDR2 Implementation Guidelines (Rev. E)PDF, 196 Кб, Версия: E, Файл опубликован: 1 авг 2012

This application report contains implementation instructions for the DDR2 interface contained on the TMS320C6472/TMS320TCI6486 DSP devices. The approach to specifying interface timing for the DDR2 interface is quite different than on previous devices.The previous approach specified device timing in terms of data sheet specifications and simulation models. The customer was required to obtain c - EMAC Implementation Guide for the TMS320C6472/TMS320TCI6486 (Rev. A)PDF, 982 Кб, Версия: A, Файл опубликован: 29 окт 2009

The TMS320TCI6486/TMS320C6472 device contains two independent Ethernet MAC modules, EMAC0 and EMAC1, and a shared MDIO controller. This document describes system implementation details of the EMAC and MDIO modules on TCI6486/C6472 device. For a detailed functional description of the EMAC/MDIO modules such as architecture and operation as well as register definitions, see the TMS320C6472/TMS32 - Power-On Self Test for the TMS320C6472/TMS320TCI6486 (Rev. A)PDF, 118 Кб, Версия: A, Файл опубликован: 29 окт 2009

This Power-On Self Test (POST) is designed to verify the operation of the TMS320TCI6486/TMS320C6472. Ten modules are included in this test: Chk6xTest, MemoryEdmaTest, TimerTest, TsipTest, I2cTest, SrioTest, EmacTest, MdioTest, and MultigemTest. These modules check the proper operation of the CPU cores, internal memory, cache operations, and several on-chip peripherals: EDMA3, Timers, TSIP, PLLs, S - TMS320C6472 Fixed-Point Digital Signal Processor Technical Brief (Rev. B)PDF, 137 Кб, Версия: B, Файл опубликован: 1 июл 2011

- Throughput Application Report for the TMS320C6472/TMS320TCI6486 (Rev. A)PDF, 403 Кб, Версия: A, Файл опубликован: 29 окт 2009

The TMS320C6472/TMS320TCI6486 has six C64x+ Megamodule cores that run at 500 MHz, 625 MHz, or 700 MHz. This document has been written based on the performance of the C6472/TCI6486 device running at 500 MHz and 625 MHz. Each megamodule has 32KB of L1D SRAM, 32KB of L1P SRAM, and 608KB of LL2 SRAM and all six cores share 768KB of SL2 SRAM. A 32-bit 533-MHz DDR2 SDRAM interface is provided on the DSP - Using Advanced Event Triggering to Debug Real-Time Problems in Embedded SystemsPDF, 919 Кб, Файл опубликован: 17 май 2002

As more and more system components become embedded within the system processor chip, new techniques are required for debug. Signals and busses that were historically available for probe connection at external package pins, are now hidden from the users within the processor package. This problem is referred to as vanishing visibility meaning that the user can no longer employ traditional techniques - Serial RapidIO Implementation Guidelines for the TMS320C6472/TMS320TCI6486 (Rev. A)PDF, 73 Кб, Версия: A, Файл опубликован: 29 окт 2009

This application report contains implementation instructions for the Serial RapidIOВ® (SRIO) interface on the TMS320TCI6486/TMS320C6472 DSP device. The approach to specifying interface timing and physical requirements for the SRIO interface is quite different than previous approaches for other interfaces.Serial RapidIO is an industry-standard, high-speed, switched-packet interconnect. Phys - Hardware Design Guide for the TMS320C6472/TMS320TCI6486 (Rev. B)PDF, 322 Кб, Версия: B, Файл опубликован: 26 окт 2009

This application report describes system design considerations for the TMS320C6472/TMS320TCI6486 (C6472/TCI6486) Digital Signal Processor (DSP). The objective of this document is to simplify the design of the C6472/TCI6486 device into a system/board design. In some cases, there is information overlapping with the TMS320TCI6486 Communications Infrastructure data manual (TMS320C6472 Power Consumption Summary (Rev. A)PDF, 58 Кб, Версия: A, Файл опубликован: 17 сен 2010

This document discusses the power consumption of the Texas Instruments TMS320C6472 digital signal processor (DSP). The power consumption on the TMS320C6472 device is highly application-dependent; therefore, a power spreadsheet that estimates power consumption is provided along with this application report. This spreadsheet can be used to model power consumption for user applications such as powEDMA v3.0 (EDMA3) Migration Guide for TMS320TCI648x DSPPDF, 345 Кб, Файл опубликован: 23 дек 2005

The TMS320TCI648x devices introduce a newly designed Enhanced Direct Memory Access (EDMA3). The EDMA3 has many new features that improve system performance and enhance debugging capabilities. This document summarizes the key differences between EDMA3 on the TMS320TCI648x devices and EDMA2 on the TMS320C64x devices. This document also provides guidance for migrating from EDMA2 to EDMA3.TMS320C6472 5V Input Pwr Design, Integrated FET DC/DC Converters and ControllersPDF, 452 Кб, Файл опубликован: 26 мар 2010

This reference design is intended for designers who wish to design up to eight TMS320C6472 Digital Signal Processors into a system using a nominal input voltage of 5 V, with a flexible design using external FETs, and low-dropout regulators for the low-power rails.Power Ref Design for TMS320C6472 5Vin DC/DC Converters (1x C6472)PDF, 251 Кб, Файл опубликован: 31 мар 2010

This reference design is intended for designers who wish to design a TMS320C6472 Digital Signal Processor into a system using a nominal input voltage of 5 V, DC/DC converters with integrated FETs, and allowing for ease-of-design and a smaller solution size.'C6472 12Vin Flexible Pwr Design Using DCDC Controllers and LDOs (8x C6472)PDF, 441 Кб, Файл опубликован: 26 мар 2010

This reference design is intended for designers who wish to design up to eight TMS320C6472 Digital Signal Processors into a system using a nominal input voltage of 12 V, external FETs for design flexibility, and low-dropout regulators for the low-power rails.Power Ref Design for TMS320C6472, 12-Vin Digital Pwr Cntrlrs, and LDOs (Rev. A)PDF, 559 Кб, Версия: A, Файл опубликован: 24 май 2010

This design was created to help those wanting to design a TMS320C6472 digital signal processor into a system using a nominal input of 12 V, having a highly flexible power design, and the ability to monitor temperature as well as dynamically monitoring and controlling voltage and current.Pwr Ref Design f/'C6472 12-Vin Digital Pwr Controllers and LDOsPDF, 558 Кб, Файл опубликован: 28 апр 2010

This design was created to help designers wishing to design up to eight TMS320C6472 Digital Signal Processors into a system using a nominal input voltage of 12 V, having a highly flexible power design, the ability to monitor temperature, and dynamically monitor and control voltage and current.Power Reference Design for the 'C6472 12V DCDC Controllers and LDOsPDF, 245 Кб, Файл опубликован: 26 мар 2010

This reference design is intended for designers who wish to design a TMS320C6472 Digital Signal Processor into a system using a nominal input voltage of 12 V external FETs for design flexibility and low-dropout regulators for the low-power rails.Error Detection and Correction Mechanism of TMS320C64x+/C674x (Rev. A)PDF, 80 Кб, Версия: A, Файл опубликован: 19 июл 2013

This application report describes the error detection and correction mechanism of the C64x+/C674x megamodule L1P and L2 memories implemented on some devices. Depending on the type of application, these mechanisms are used to either provide diagnostic measures to detect faults in the memory that could lead to unacceptable risk for the user or to increase the availability of the system.Multicore Programming Guide (Rev. B)PDF, 1.8 Мб, Версия: B, Файл опубликован: 29 авг 2012

As application complexity continues to grow, we have reached a limit on increasing performance by merely scaling clock speed. To meet the ever-increasing processing demand, modern System-On-Chip solutions contain multiple processing cores. The dilemma is how to map applications to multicore devices. In this paper, we present a programming methodology for converting applications to run on multicoreUsing IBIS Models for Timing Analysis (Rev. A)PDF, 301 Кб, Версия: A, Файл опубликован: 15 апр 2003

Today?s high-speed interfaces require strict timings and accurate system design. To achieve the necessary timings for a given system, input/output buffer information specification (IBIS) models must be used. These models accurately represent the device drivers under various process conditions. Board characteristics, such as impedance, loading, length, number of nodes, etc., affect how the device dTMS320C64x to TMS320C64x+ CPU Migration Guide (Rev. A)PDF, 310 Кб, Версия: A, Файл опубликован: 20 окт 2005

This document describes migration from the Texas Instruments TMS320C64xв„ў digital signal processor (DSP) to the TMS320C64x+в„ў DSP. The objective of this document is to indicate differences between the two cores and to briefly describe new features. Functionality in the devices that is identical is not included. For detailed information about either device, see the TMS320C64x/C64x+ DSPIntroduction to TMS320C6000 DSP OptimizationPDF, 535 Кб, Файл опубликован: 6 окт 2011

The TMS320C6000™ Digital Signal Processors (DSPs) have many architectural advantages that make them ideal for computation-intensive real-time applications. However to fully leverage the architectural features that C6000™ processors offer code optimization may be required. First this document reviews five key concepts in understanding the C6000 DSP architecture and optimization. ThenМодельный ряд

Серия: TMS320C6472 (8)Классификация производителя

- Semiconductors> Processors> Digital Signal Processors> C6000 DSP> Other C6000 DSP

На английском языке: Datasheet Texas Instruments TMS320C6472