Datasheet SAM4E (Microchip) - 1445

| Производитель | Microchip |

| Описание | Atmel | SMART ARM-based Flash MCU |

| Страниц / Страница | 1461 / 1445 |

| Формат / Размер файла | PDF / 6.4 Мб |

| Язык документа | английский |

Модельный ряд для этого даташита

Текстовая версия документа

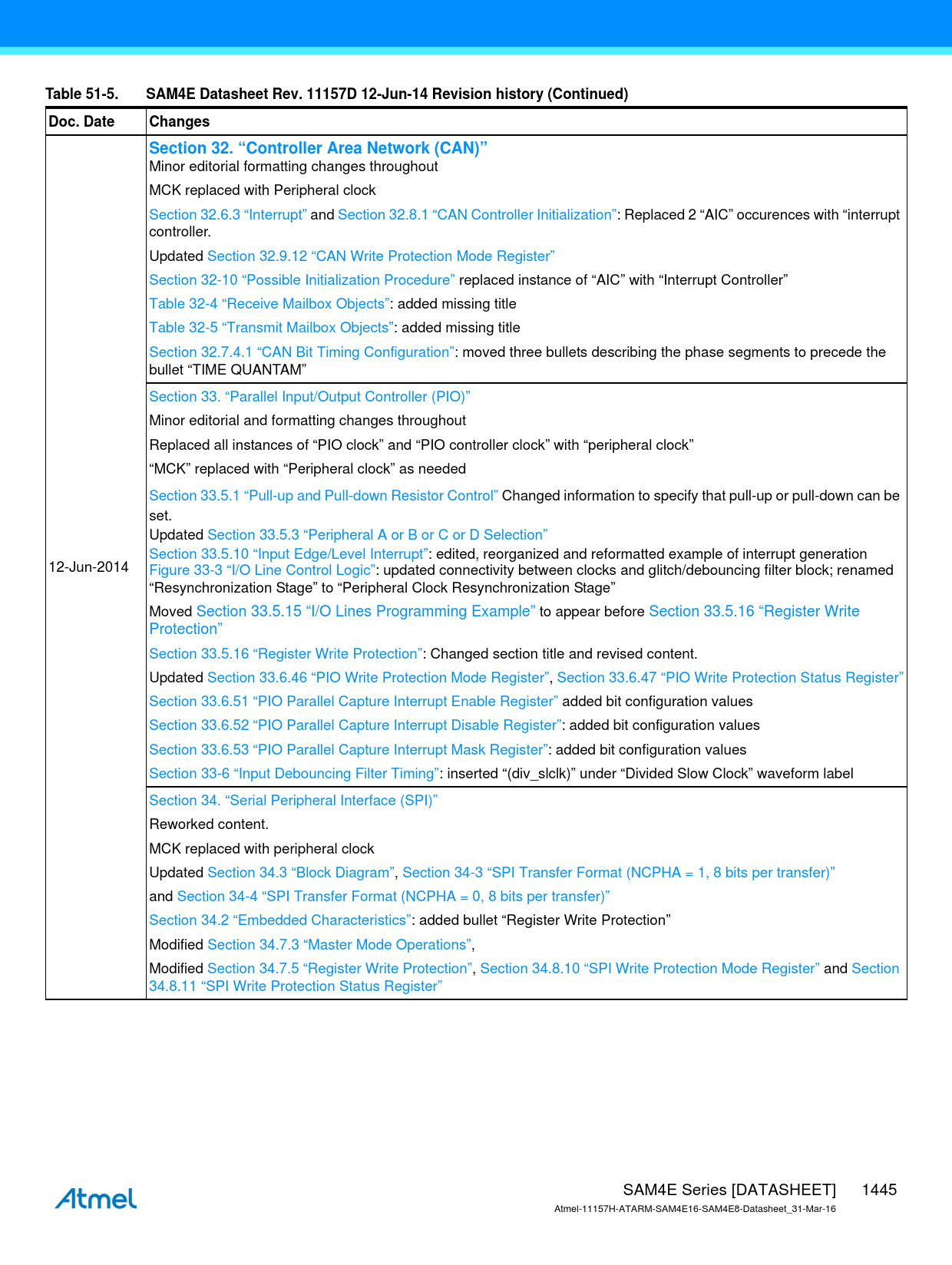

Table 51-5. SAM4E Datasheet Rev. 11157D 12-Jun-14 Revision history (Continued) Doc. Date Changes Section 32. “Controller Area Network (CAN)”

Minor editorial formatting changes throughout

MCK replaced with Peripheral clock

Section 32.6.3 “Interrupt” and Section 32.8.1 “CAN Controller Initialization”: Replaced 2 “AIC” occurences with “interrupt

controller.

Updated Section 32.9.12 “CAN Write Protection Mode Register”

Section 32-10 “Possible Initialization Procedure” replaced instance of “AIC” with “Interrupt Controller”

Table 32-4 “Receive Mailbox Objects”: added missing title

Table 32-5 “Transmit Mailbox Objects”: added missing title

Section 32.7.4.1 “CAN Bit Timing Configuration”: moved three bullets describing the phase segments to precede the

bullet “TIME QUANTAM”

Section 33. “Parallel Input/Output Controller (PIO)”

Minor editorial and formatting changes throughout

Replaced all instances of “PIO clock” and “PIO controller clock” with “peripheral clock”

“MCK” replaced with “Peripheral clock” as needed 12-Jun-2014 Section 33.5.1 “Pull-up and Pull-down Resistor Control” Changed information to specify that pull-up or pull-down can be

set.

Updated Section 33.5.3 “Peripheral A or B or C or D Selection”

Section 33.5.10 “Input Edge/Level Interrupt”: edited, reorganized and reformatted example of interrupt generation

Figure 33-3 “I/O Line Control Logic”: updated connectivity between clocks and glitch/debouncing filter block; renamed

“Resynchronization Stage” to “Peripheral Clock Resynchronization Stage”

Moved Section 33.5.15 “I/O Lines Programming Example” to appear before Section 33.5.16 “Register Write

Protection”

Section 33.5.16 “Register Write Protection”: Changed section title and revised content.

Updated Section 33.6.46 “PIO Write Protection Mode Register”, Section 33.6.47 “PIO Write Protection Status Register”

Section 33.6.51 “PIO Parallel Capture Interrupt Enable Register” added bit configuration values

Section 33.6.52 “PIO Parallel Capture Interrupt Disable Register”: added bit configuration values

Section 33.6.53 “PIO Parallel Capture Interrupt Mask Register”: added bit configuration values

Section 33-6 “Input Debouncing Filter Timing”: inserted “(div_slclk)” under “Divided Slow Clock” waveform label

Section 34. “Serial Peripheral Interface (SPI)”

Reworked content.

MCK replaced with peripheral clock

Updated Section 34.3 “Block Diagram”, Section 34-3 “SPI Transfer Format (NCPHA = 1, 8 bits per transfer)”

and Section 34-4 “SPI Transfer Format (NCPHA = 0, 8 bits per transfer)”

Section 34.2 “Embedded Characteristics”: added bullet “Register Write Protection”

Modified Section 34.7.3 “Master Mode Operations”,

Modified Section 34.7.5 “Register Write Protection”, Section 34.8.10 “SPI Write Protection Mode Register” and Section

34.8.11 “SPI Write Protection Status Register” SAM4E Series [DATASHEET]

Atmel-11157H-ATARM-SAM4E16-SAM4E8-Datasheet_31-Mar-16 1445

Купить ATSAM4E8CA-ANR на РадиоЛоцман.Цены — от 372 до 706 ₽

Купить ATSAM4E8CA-ANR на РадиоЛоцман.Цены — от 372 до 706 ₽