Datasheet ADSP-21483, ADSP-21486, ADSP-21487, ADSP-21488, ADSP-21489 (Analog Devices) - 71

| Производитель | Analog Devices |

| Описание | SHARC Processor |

| Страниц / Страница | 71 / 71 — ADSP-21483/ADSP-21486/ADSP-21487/ADSP-21488/ADSP-21489. Processor … |

| Версия | H |

| Формат / Размер файла | PDF / 1.9 Мб |

| Язык документа | английский |

ADSP-21483/ADSP-21486/ADSP-21487/ADSP-21488/ADSP-21489. Processor Instruction. Model1, 2. Notes. Temperature Range3. RAM

Модельный ряд для этого даташита

Текстовая версия документа

link to page 18 link to page 71

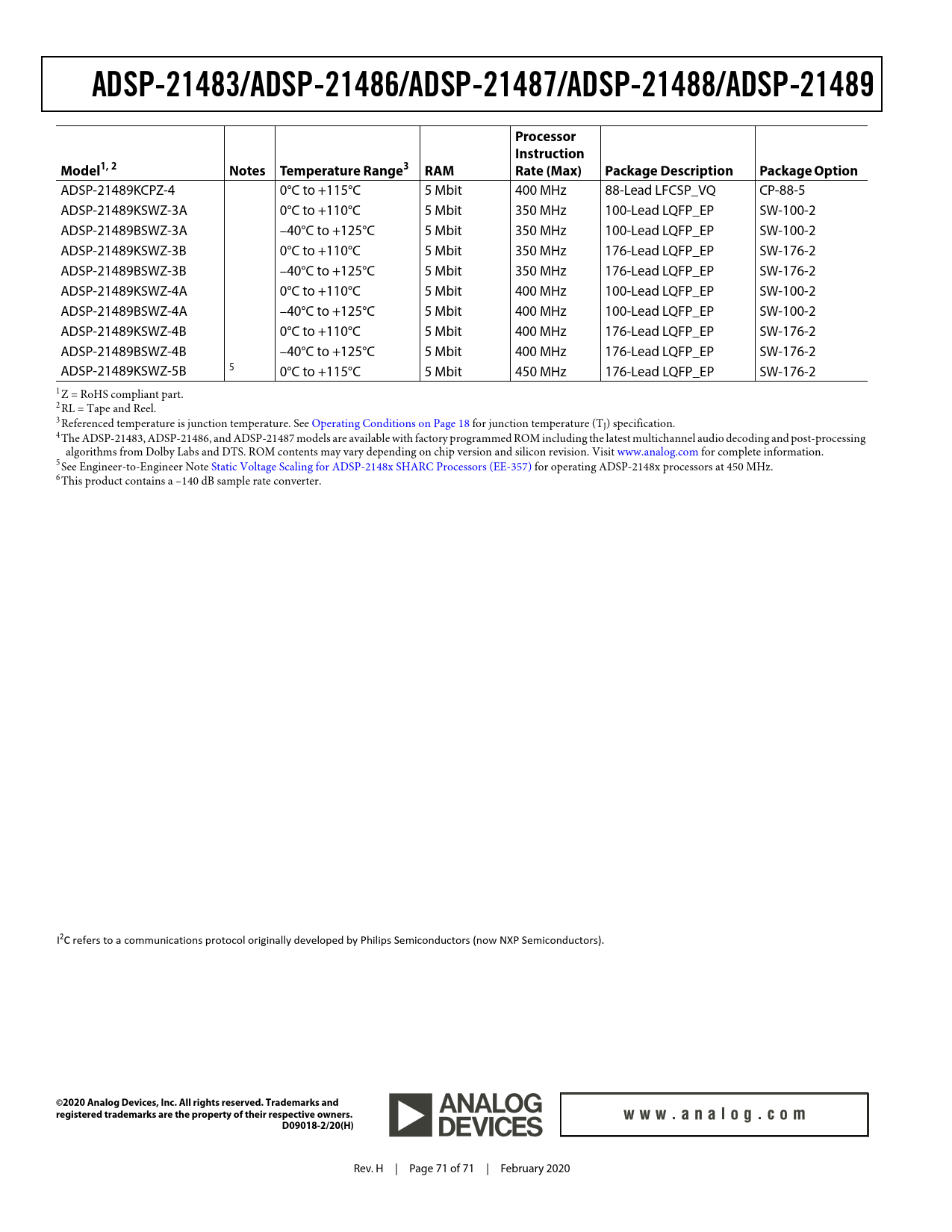

ADSP-21483/ADSP-21486/ADSP-21487/ADSP-21488/ADSP-21489 Processor Instruction Model1, 2 Notes Temperature Range3 RAM Rate (Max) Package Description Package Option

ADSP-21489KCPZ-4 0°C to +115°C 5 Mbit 400 MHz 88-Lead LFCSP_VQ CP-88-5 ADSP-21489KSWZ-3A 0°C to +110°C 5 Mbit 350 MHz 100-Lead LQFP_EP SW-100-2 ADSP-21489BSWZ-3A –40°C to +125°C 5 Mbit 350 MHz 100-Lead LQFP_EP SW-100-2 ADSP-21489KSWZ-3B 0°C to +110°C 5 Mbit 350 MHz 176-Lead LQFP_EP SW-176-2 ADSP-21489BSWZ-3B –40°C to +125°C 5 Mbit 350 MHz 176-Lead LQFP_EP SW-176-2 ADSP-21489KSWZ-4A 0°C to +110°C 5 Mbit 400 MHz 100-Lead LQFP_EP SW-100-2 ADSP-21489BSWZ-4A –40°C to +125°C 5 Mbit 400 MHz 100-Lead LQFP_EP SW-100-2 ADSP-21489KSWZ-4B 0°C to +110°C 5 Mbit 400 MHz 176-Lead LQFP_EP SW-176-2 ADSP-21489BSWZ-4B –40°C to +125°C 5 Mbit 400 MHz 176-Lead LQFP_EP SW-176-2 ADSP-21489KSWZ-5B 5 0°C to +115°C 5 Mbit 450 MHz 176-Lead LQFP_EP SW-176-2 1 Z = RoHS compliant part. 2 RL = Tape and Reel. 3 Referenced temperature is junction temperature. See Operating Conditions on Page 18 for junction temperature (TJ) specification. 4 The ADSP-21483, ADSP-21486, and ADSP-21487 models are available with factory programmed ROM including the latest multichannel audio decoding and post-processing algorithms from Dolby Labs and DTS. ROM contents may vary depending on chip version and silicon revision. Visit www.analog.com for complete information. 5 See Engineer-to-Engineer Note Static Voltage Scaling for ADSP-2148x SHARC Processors (EE-357) for operating ADSP-2148x processors at 450 MHz. 6 This product contains a –140 dB sample rate converter. I2C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

©2020 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D09018-2/20(H)

Rev. H | Page 71 of 71 | February 2020 Document Outline Features Table of Contents Revision History General Description Family Core Architecture SIMD Computational Engine Independent, Parallel Computation Units Timer Data Register File Context Switch Universal Registers Single-Cycle Fetch of Instruction and Four Operands Instruction Cache Data Address Generators With Zero-Overhead Hardware Circular Buffer Support Flexible Instruction Set Variable Instruction Set Architecture (VISA) On-Chip Memory ROM Based Security On-Chip Memory Bandwidth Family Peripheral Architecture External Memory External Port Asynchronous Memory Controller SDRAM Controller SIMD Access to External Memory VISA and ISA Access to External Memory Pulse-Width Modulation MediaLB Digital Applications Interface (DAI) Serial Ports (SPORTs) S/PDIF-Compatible Digital Audio Receiver/Transmitter Asynchronous Sample Rate Converter (SRC) Input Data Port Precision Clock Generators Digital Peripheral Interface (DPI) Serial Peripheral (Compatible) Interface (SPI) UART Port Timers 2-Wire Interface Port (TWI) I/O Processor Features DMA Controller Delay Line DMA Scatter/Gather DMA FFT Accelerator FIR Accelerator IIR Accelerator Watchdog Timer System Design Program Booting Power Supplies Static Voltage Scaling (SVS) Target Board JTAG Emulator Connector Development Tools Integrated Development Environments (IDEs) EZ-KIT Lite Evaluation Board EZ-KIT Lite Evaluation Kits Software Add-Ins for CrossCore Embedded Studio Board Support Packages for Evaluation Hardware Middleware Packages Algorithmic Modules Designing an Emulator-Compatible DSP Board (Target) Additional Information Related Signal Chains Pin Function Descriptions Specifications Operating Conditions Electrical Characteristics Total Power Dissipation Absolute Maximum Ratings ESD Sensitivity Maximum Power Dissipation Timing Specifications Core Clock Requirements Voltage Controlled Oscillator (VCO) Power-Up Sequencing Clock Input Clock Signals Reset Running Reset Interrupts Core Timer Timer PWM_OUT Cycle Timing Timer WDTH_CAP Timing Watchdog Timer Timing Pin to Pin Direct Routing (DAI and DPI) Precision Clock Generator (Direct Pin Routing) Flags SDRAM Interface Timing (166 MHz SDCLK) AMI Read AMI Write Serial Ports Input Data Port (IDP) Parallel Data Acquisition Port (PDAP) Sample Rate Converter—Serial Input Port Sample Rate Converter—Serial Output Port Pulse-Width Modulation Generators (PWM) S/PDIF Transmitter S/PDIF Transmitter-Serial Input Waveforms S/PDIF Transmitter Input Data Timing Oversampling Clock (TxCLK) Switching Characteristics S/PDIF Receiver Internal Digital PLL Mode SPI Interface—Master SPI Interface—Slave Media Local Bus Universal Asynchronous Receiver-Transmitter (UART) Ports—Receive and Transmit Timing 2-Wire Interface (TWI)—Receive and Transmit Timing JTAG Test Access Port and Emulation Output Drive Currents Test Conditions Capacitive Loading Thermal Characteristics Thermal Diode 88-Lead LFCSP_VQ Lead Assignment 100-Lead LQFP_EP Lead Assignment 176-Lead LQFP_EP Lead Assignment Outline Dimensions Surface-Mount Design Automotive Products Ordering Guide