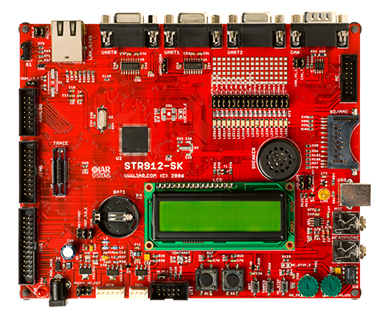

Внутрисхемный эмулятор IAR KSDKSTR912 J-LINK

KSDKSTR912 J-LINK – оценочная плата фирмы IAR позволяет разрабатывать и тестировать ПО для микроконтроллеров серии STR91x от STMicroelectronics, а также определять требования к программной и аппаратной части будущего изделия на этапе макетирования.

Подробное описание

Отличительные особенности:

- установленный микроконтроллер STR912FW44X: ARM966E-S 96 MГц, 512 КБайт + 32 КБайт Flash-память программ, 96 КБайт ОЗУ, внешняя шина, девять каналов DMA, 10-разрядный АЦП, 10/100 Mбит Ethernet MAC, 3 UART, USB 2.0;

- интерфейс USB 2.0 Full Speed;

- Ethernet интерфейс на базе ИМС STE100P;

- ЖКИ 16×2;

- держатель батареи часов реального времени;

- аудио-интерфейс;

- периферия пользователя: кнопки, светодиоды и потенциометры;

- порт CAN;

- три порта RS-232;

- вход АЦП;

- отладочный интерфейс JTAG и TRACE.

Основные параметры

|

Параметр |

Значение |

|

Интерфейс подключения |

USB / ARM-JTAG / TRACE |

|

Ядро базового компонента |

ARM966E-S |

|

Разрядность, бит |

32 |

|

Базовый компонент |

STR912FW44X |

|

Вспомогательный компонент |

STE100P |

|

Целевое напряжение, В |

1.8 / 3.3 / 5.0 |

|

Напряжение питания, В |

9.0 / 5.0 |

|

Источник питания |

внешний / USB |

Комплектация:

- отладочная плата KSDKSTR912;

- USB-JTAG эмулятор J-LINK;

- компакт-диск с документацией, исходными кодами;

- руководство по быстрому старту.

Принципиальная схема отладочной платы

Варианты написания:

KSDKSTR912 JLINK, KSDKSTR912 J LINK