Во многих приложениях, в которых используется цифровой синтез трехфазных синусоидальных сигналов, таких как приводы двигателей переменного тока, фильтры активной мощности и синхронизаторы сети, цифровое управление реализуется с помощью микроконтроллера или DSP. Синтез может выполняться с использованием традиционных аналоговых технологий [1] или DDS (direct digital synthesis, прямой цифровой синтез). Цифровые технологии обеспечивают более высокую стабильность и возможность регулировки частоты, фазы и амплитуды. В приложениях, требующих синтеза трехфазного сигнала с разрешением 16 бит и выше, DDS предполагает использование микропроцессора или DSP для взаимодействия с несколькими ЦАП. При таком подходе используется не только большое количество основных устройств, но и вспомогательных компонентов, которые занимают много места на печатной плате. Хотя один ЦАП может иметь несколько каналов с последовательным управлением – четыре, восемь, 32 или более, – большое количество каналов обеспечивается за счет низкой разрядности ЦАП. Поэтому использование многоканальных ЦАП является непривлекательным подходом.

В качестве альтернативы можно использовать сдвиговые регистры или фильтры на переключаемых конденсаторах, но для такого подхода также нужно большое количество компонентов, а отсутствие регулировки фазы и амплитуды делает этот метод непригодным для DDS высокого разрешения [2]. В то же время стереофонические ЦАП легко доступны. Эти высококачественные компоненты недороги благодаря их широкому применению и массовому производству. Например, микросхема UDA1330ATS имеет последовательный интерфейс I2S, длину слова 16, 18 и 20 бит, частоту дискретизации от 8 до 55 кГц. Эти особенности делают такие ЦАП привлекательными для трехфазных DDS с небольшим количеством компонентов.

В предлагаемой здесь схеме (Рисунок 1) реализована технология DDS с использованием микроконтроллера ARM (IC1), одного стерео ЦАП (IC2) и одного операционного усилителя (IC3). Код микроконтроллера ARM AT91SAM7X256, приведенный в Листинге 1, формирует таблицу, содержащую косинусную функцию нужного разрешения и длины. Таблица заполняется значениями cos(α + 2/3π) и cos(α – 2/3π). Микроконтроллер ARM отправляет данные в последовательном формате стандарта I2S с помощью процедуры обслуживания прерываний, запускаемой всякий раз, когда выходной буфер пуст. Обработчик прерываний для отправки данных содержится в Листинге 2. Микросхема IC2 формирует выходные напряжения VA и VB – два из трех сигналов – с максимальной амплитудой 5 В пик-пик, но со смещением 2.5 В. Третий канал VC можно получить как функцию от двух других каналов. Эту операцию можно легко реализовать с помощью одного инвертирующего суммирующего операционного усилителя IC3 и опорного напряжения ЦАП 2.5 В для компенсации смещения. В этом случае для получения единичного усиления должно выполняться соотношение RF = RA = RB = 10 кОм, а для точной компенсации смещения при отклонении сопротивлений резисторов можно добавить потенциометр на инвертирующий вход.

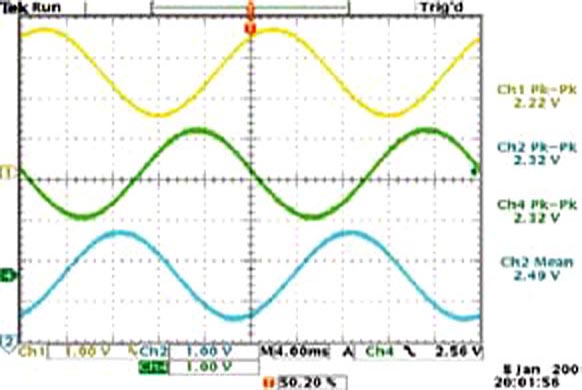

На Рисунке 2 показан результат синтеза трехфазных сигналов VA, VB и VC. При проектировании следует иметь в виду, что из-за использования интерфейса I2S выходные сигналы имеют присущую им фазовую задержку. Для аудиоприложений этой задержкой, составляющей ровно 1/fs (fs – частота выборки), можно пренебречь, но в системах питания она может иметь значение. Прямой подход к устранению задержки заключается в синтезе второго канала с отрицательной фазовой задержкой, компенсирующей его собственную задержку. Из Рисунка 2 видно, что фазовая задержка между выходными каналами отсутствует, за исключением относительного сдвига 120° между ними. Поскольку для этого необходима только относительная разность фаз 120°, на выходе можно получать сигналы, отличные от чистой синусоиды.

|

|

| Рисунок 2. | Осциллограммы 1 и 2 показывают напряжения на выходах ЦАП. Осциллограмма 4 – это третий канал, который обеспечивается инвертирующим суммирующим операционным усилителем. |

Ссылки

- Al Dutcher. Трехфазный ГУН на основе инверторов.

- Perez-Lobato, Eduardo, “Three-phase sinusoidal-waveform generator uses PLD.”

Загрузки

- Листинг 1. Код формирования таблицы косинусной функции

- Листинг 2. Обработчик прерываний для отправки данных

Купить UDA1330ATS на РадиоЛоцман.Цены

Купить UDA1330ATS на РадиоЛоцман.Цены