Datasheet 1508МТ015, К1508МТ015, К1508МТ015К, 1508МТ01Н4, К1508МТ01Н4 (Миландр) - 8

| Производитель | Миландр |

| Описание | Микросхема синтезатора частот с дробным коэффициентом деления и встроенным генератором, управляемым напряжением |

| Страниц / Страница | 42 / 8 — Спецификация 1508МТ015, К1508МТ015, К1508МТ015К, 1508МТ01Н4, К1508МТ01Н4. … |

| Формат / Размер файла | PDF / 1.4 Мб |

| Язык документа | английский |

Спецификация 1508МТ015, К1508МТ015, К1508МТ015К, 1508МТ01Н4, К1508МТ01Н4. MODSEL<1:0>. Описание режима. 5.2

Модельный ряд для этого даташита

Текстовая версия документа

link to page 26 link to page 8 link to page 9

Спецификация 1508МТ015, К1508МТ015, К1508МТ015К, 1508МТ01Н4, К1508МТ01Н4

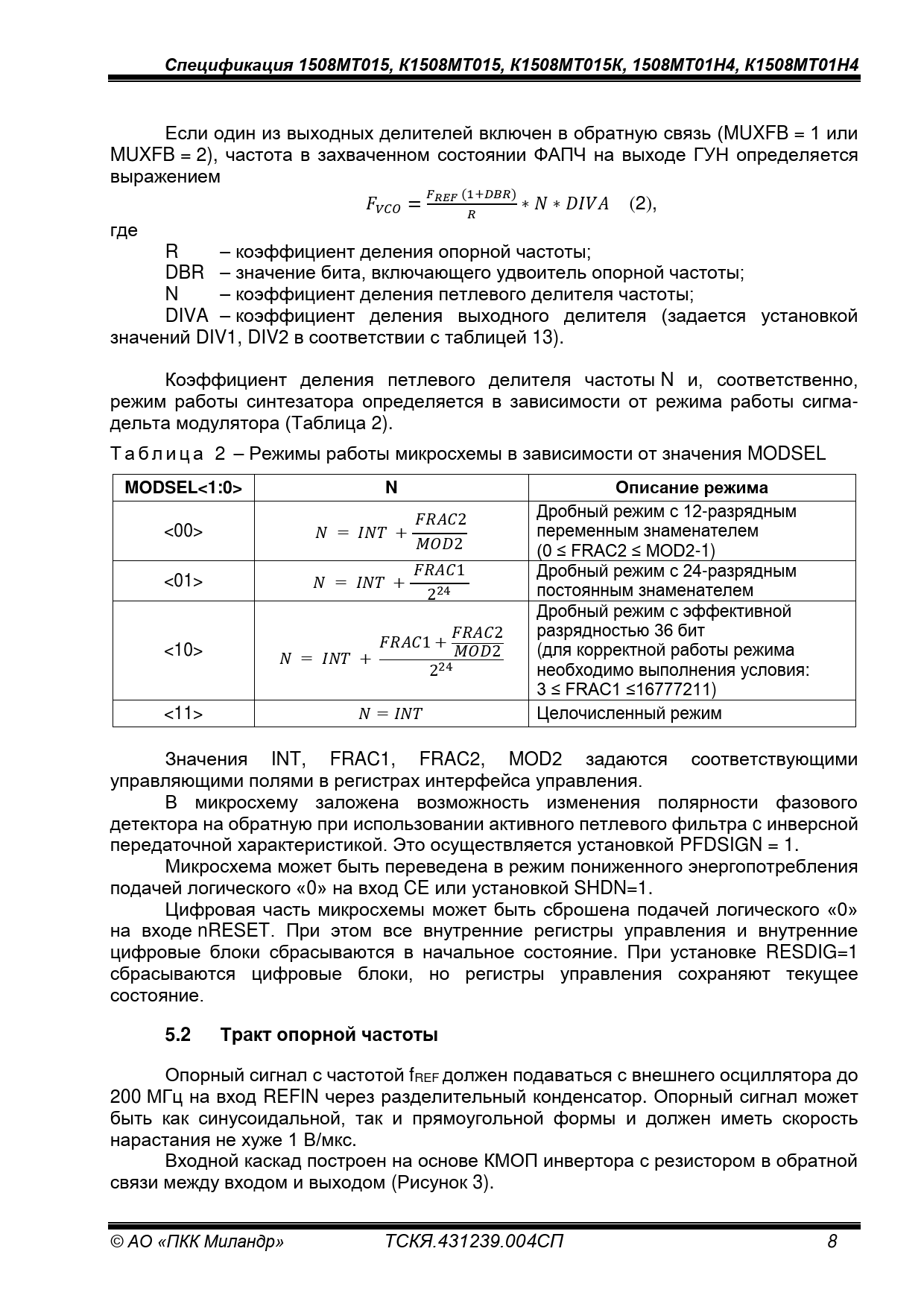

Если один из выходных делителей включен в обратную связь (MUXFB = 1 или MUXFB = 2), частота в захваченном состоянии ФАПЧ на выходе ГУН определяется выражением 𝐹𝑉𝐶𝑂 = 𝐹𝑅𝐸𝐹 (1+𝐷𝐵𝑅) ∗ 𝑁 ∗ 𝐷𝐼𝑉𝐴 (2), 𝑅 где R – коэффициент деления опорной частоты; DBR – значение бита, включающего удвоитель опорной частоты; N – коэффициент деления петлевого делителя частоты; DIVA – коэффициент деления выходного делителя (задается установкой значений DIV1, DIV2 в соответствии с таблицей 13). Коэффициент деления петлевого делителя частоты N и, соответственно, режим работы синтезатора определяется в зависимости от режима работы сигма- дельта модулятора (Таблица 2). Т а б л и ц а 2 – Режимы работы микросхемы в зависимости от значения MODSEL

MODSEL<1:0> N Описание режима

𝐹𝑅𝐴𝐶2 Дробный режим с 12-разрядным <00> 𝑁 = 𝐼𝑁𝑇 + переменным знаменателем 𝑀𝑂𝐷2 (0 ≤ FRAC2 ≤ MOD2-1) 𝐹𝑅𝐴𝐶1 Дробный режим с 24-разрядным <01> 𝑁 = 𝐼𝑁𝑇 + 224 постоянным знаменателем Дробный режим с эффективной 𝐹𝑅𝐴𝐶2 разрядностью 36 бит 𝐹𝑅𝐴𝐶1 + <10> 𝑁 = 𝐼𝑁𝑇 + 𝑀𝑂𝐷2 (для корректной работы режима 224 необходимо выполнения условия: 3 ≤ FRAC1 ≤16777211) <11> 𝑁 = 𝐼𝑁𝑇 Целочисленный режим Значения INT, FRAC1, FRAC2, MOD2 задаются соответствующими управляющими полями в регистрах интерфейса управления. В микросхему заложена возможность изменения полярности фазового детектора на обратную при использовании активного петлевого фильтра c инверсной передаточной характеристикой. Это осуществляется установкой PFDSIGN = 1. Микросхема может быть переведена в режим пониженного энергопотребления подачей логического «0» на вход CE или установкой SHDN=1. Цифровая часть микросхемы может быть сброшена подачей логического «0» на входе nRESET. При этом все внутренние регистры управления и внутренние цифровые блоки сбрасываются в начальное состояние. При установке RESDIG=1 сбрасываются цифровые блоки, но регистры управления сохраняют текущее состояние.

5.2 Тракт опорной частоты

Опорный сигнал с частотой fREF должен подаваться с внешнего осциллятора до 200 МГц на вход REFIN через разделительный конденсатор. Опорный сигнал может быть как синусоидальной, так и прямоугольной формы и должен иметь скорость нарастания не хуже 1 В/мкс. Входной каскад построен на основе КМОП инвертора с резистором в обратной связи между входом и выходом (Рисунок 3). © АО «ПКК Миландр» ТСКЯ.431239.004CП 8 Document Outline 1 Структурная блок-схема микросхемы 2 Условное графическое обозначение 3 Описание выводов 4 Указания по применению и эксплуатации 5 Описание функционирования микросхемы 5.1 Общее описание микросхемы 5.2 Тракт опорной частоты 5.3 Петлевой делитель частоты 5.4 Фазовый детектор и зарядно-разрядный блок 5.4.1 Ток смещения ЗРБ 5.5 Генератор, управляемый напряжением 5.6 Система автоматической установки диапазона ГУН 5.7 Работа в режиме с отключенной автокалибровкой и непосредственной установкой рабочего диапазона ГУН 5.8 Выходные делители частоты, выходы RF, CMOS, LVDS 5.9 Детектор захвата частоты 5.10 Универсальный выход MUXOUT 5.11 Функция быстрого захвата частоты (Fast Lock) 5.12 Функция предотвращения «проскальзывания» циклов (CSR – Cycle Slip Reduction) 5.13 Отключение буферов выходного сигнала 5.14 Фазовый шум и паразитные составляющие спектра выходного сигнала в дробных режимах работы 5.15 Функция управления фазой выходного сигнала 5.16 Ток потребления в различных режимах работы 5.17 Процедура включения и начальное состояние микросхемы 5.18 Описание протокола интерфейса программирования 5.18.1 Запись регистров управления 5.18.2 Чтение внутренних регистров состояния 5.19 Карта регистров SPI-интерфейса 6 Типовая схема включения микросхемы 7 Предельно-допустимые характеристики микросхемы 8 Электрические параметры микросхемы 9 Справочные данные 10 Основные зависимости 11 Габаритный чертеж микросхемы 12 Информация для заказа 13 Лист регистрации изменений