Datasheet 1508МТ015, К1508МТ015, К1508МТ015К, 1508МТ01Н4, К1508МТ01Н4 (Миландр) - 9

| Производитель | Миландр |

| Описание | Микросхема синтезатора частот с дробным коэффициентом деления и встроенным генератором, управляемым напряжением |

| Страниц / Страница | 42 / 9 — Спецификация 1508МТ015, К1508МТ015, К1508МТ015К, 1508МТ01Н4, К1508МТ01Н4. … |

| Формат / Размер файла | PDF / 1.4 Мб |

| Язык документа | английский |

Спецификация 1508МТ015, К1508МТ015, К1508МТ015К, 1508МТ01Н4, К1508МТ01Н4. VCCA1. Ко входу фазового. детектора. MUX2

Модельный ряд для этого даташита

Текстовая версия документа

link to page 9 link to page 9

Спецификация 1508МТ015, К1508МТ015, К1508МТ015К, 1508МТ01Н4, К1508МТ01Н4

Опорный сигнал может поступать без деления на вход фазового детектора, либо проходить через делитель частоты с коэффициентом деления от 1 до 4095. Также есть возможность использовать умножитель частоты на 2. Удвоитель частоты задействуется установкой DBR = 1. Частота на выходе делителя частоты (частота фазового детектора) не должна превышать 100 МГц для целочисленного режима работы и 50 МГц для дробных режимов.

VCCA1 Ко входу фазового детектора MUX2 Делитель опорной частоты удвоитель REFIN частоты R<11:0> GNDA1 DBR

Рисунок 3 – Структурная схема тракта опорной частоты

5.3 Петлевой делитель частоты Ко входу фазового Основной счетчик детектора

ЭСЛ

Вход частоты с ГУН или Усилитель

Общая

с выходных делителей частоты Прескалер 4/5

перезагрузка

Поглощающий счетчик

B<1:0>

INT<16:0>

+ A<14:0>

3 бита От сигма- дельта модулятора

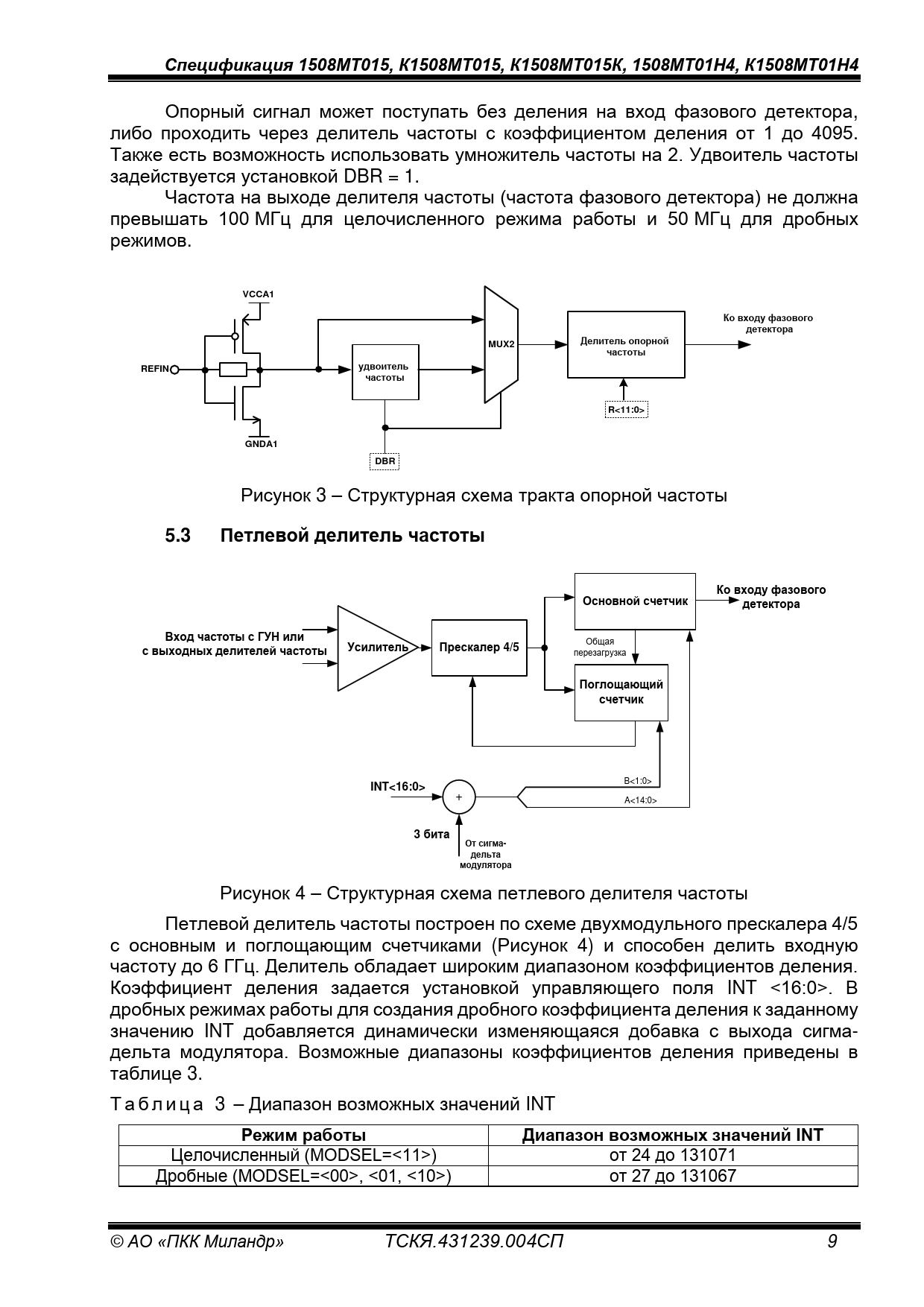

Рисунок 4 – Структурная схема петлевого делителя частоты Петлевой делитель частоты построен по схеме двухмодульного прескалера 4/5 с основным и поглощающим счетчиками (Рисунок 4) и способен делить входную частоту до 6 ГГц. Делитель обладает широким диапазоном коэффициентов деления. Коэффициент деления задается установкой управляющего поля INT <16:0>. В дробных режимах работы для создания дробного коэффициента деления к заданному значению INT добавляется динамически изменяющаяся добавка с выхода сигма- дельта модулятора. Возможные диапазоны коэффициентов деления приведены в таблице 3. Т а б л и ц а 3 – Диапазон возможных значений INT

Режим работы Диапазон возможных значений INT

Целочисленный (MODSEL=<11>) от 24 до 131071 Дробные (MODSEL=<00>, <01, <10>) от 27 до 131067 © АО «ПКК Миландр» ТСКЯ.431239.004CП 9 Document Outline 1 Структурная блок-схема микросхемы 2 Условное графическое обозначение 3 Описание выводов 4 Указания по применению и эксплуатации 5 Описание функционирования микросхемы 5.1 Общее описание микросхемы 5.2 Тракт опорной частоты 5.3 Петлевой делитель частоты 5.4 Фазовый детектор и зарядно-разрядный блок 5.4.1 Ток смещения ЗРБ 5.5 Генератор, управляемый напряжением 5.6 Система автоматической установки диапазона ГУН 5.7 Работа в режиме с отключенной автокалибровкой и непосредственной установкой рабочего диапазона ГУН 5.8 Выходные делители частоты, выходы RF, CMOS, LVDS 5.9 Детектор захвата частоты 5.10 Универсальный выход MUXOUT 5.11 Функция быстрого захвата частоты (Fast Lock) 5.12 Функция предотвращения «проскальзывания» циклов (CSR – Cycle Slip Reduction) 5.13 Отключение буферов выходного сигнала 5.14 Фазовый шум и паразитные составляющие спектра выходного сигнала в дробных режимах работы 5.15 Функция управления фазой выходного сигнала 5.16 Ток потребления в различных режимах работы 5.17 Процедура включения и начальное состояние микросхемы 5.18 Описание протокола интерфейса программирования 5.18.1 Запись регистров управления 5.18.2 Чтение внутренних регистров состояния 5.19 Карта регистров SPI-интерфейса 6 Типовая схема включения микросхемы 7 Предельно-допустимые характеристики микросхемы 8 Электрические параметры микросхемы 9 Справочные данные 10 Основные зависимости 11 Габаритный чертеж микросхемы 12 Информация для заказа 13 Лист регистрации изменений