Журнал РАДИОЛОЦМАН, февраль 2015

Steven Xie, Analog Devices

Analog Dialogue

Введение

Аналого-цифровые преобразователи (АЦП) последовательных приближений, называемые так из-за входящего в их состав регистра последовательных приближений, широко используются в приложениях, требующих разрешения до 18 бит при скорости преобразования до 5 млн. выборок в секунду. К преимуществам таких АЦП относятся небольшие размеры, низкая мощность потребления, отсутствие конвейерной задержки и простота использования.

Управляющий процессор может считывать данные из АЦП или передавать ему команды управления, используя разнообразные последовательные и параллельные интерфейсы, такие как SPI, I2C и LVDS. В этой статье обсуждаются методы проектирования надежных интегральных цифровых интерфейсов, включая уровни и последовательности включения напряжений питания, состояния входов/выходов в процессе установления напряжения, временные зависимости, качество сигналов и ошибки, порождаемые работой цифровых узлов.

Напряжение питания цифровых входов/выходов и порядок его включения

Для подключения питания цифровых входов/выходов у большинства АЦП последовательных приближений есть отдельный вход, обозначаемый VIO или VDRIVE, который и определяет параметры совместимости рабочих напряжений и логических уровней интерфейсов. Этот вывод должен находиться под тем же напряжением, от которого получают питание внешние управляющие контроллеры, ЦСП или ПЛИС. Как правило, чтобы не выйти за границы допустимых режимов, напряжение на цифровых входов должно находится в диапазоне между DGND − 0.3 В и VDRIVE + 0.3 В. Между выводами VDRIVE и DGND (цифровая земля) следует устанавливать развязывающие конденсаторы, связанные с выводами АЦП печатными проводниками минимальной длины.

В справочных данных на АЦП, питающиеся от нескольких источников, может быть четко прописана последовательность их включения. Хорошим источником информации для разработчиков систем питания подобных АЦП послужит [1]. Чтобы не допустить прямого смещения входных защитных диодов и перехода цифрового ядра в неопределенное состояние, питание входов/выходов следует включать раньше, чем питание интерфейсных цепей. Аналоговое питание обычно подается перед включением питания входов/выходов, однако это правило не является общим для всех АЦП. В любом случае, прежде чем приступить к конструированию источника питания, внимательно изучите справочную документацию.

Состояние цифровых входов/выходов во время включения

Для правильной инициализации некоторых АЦП последовательных приближений требуется соблюдение определенной последовательности логических состояний, обеспечивающих выполнение таких функций, как сброс, переход в режим пониженного энергопотребления или выключение. После установления всех питающих напряжений для гарантированного перевода АЦП в нужное исходное состояние на микросхему необходимо подать импульс или комбинацию импульсов с указанными в технической документации параметрами. Например, чтобы гарантировать нормальное функционирование микросхемы AD7606, после включения питания на вход RESET требуется подать импульс высокого уровня длительностью не менее 50 нс.

|

|

| Рисунок 1. | Подача высокого уровня на вход /CNVST во время установления напряжений питания может стать причиной неопределенного состояния АЦП. |

До полного установления напряжений питания подавать на цифровые выводы какие-либо сигналы нельзя. У АЦП последовательных приближений выводы пуска преобразования (/CNVST) могут быть чувствительны к помехам. На Рисунке 1 приведен пример, в котором управляющая ПЛИС устанавливает высокий уровень на выводе /CNVST в то время, пока еще не закончилось установление напряжений AVCC, DVCC и VDRIVE (питание аналоговой, цифровой и интерфейсной частей, соответственно). Это может перевести AD7367 в неопределенное состояние, поэтому до установления питания управляющий процессор должен удерживать на входе /CNVST низкий логический уровень.

Синхронизация цифровых интерфейсов

После завершения преобразования хост должен считать данные через последовательный интерфейс. Для корректного считывания требуется соблюдать определенные параметры временной диаграммы, зависящие, например, от выбора режима работы шины SPI. Не нарушайте указанных в спецификациях временных соотношений между сигналами интерфейса, в особенности, времена установления и удержания АЦП и хоста. Максимальная скорость передачи данных определяется полным циклом, а не только указанным в документации минимальным периодом тактовой частоты. Рисунок 2 и последующие формулы иллюстрируют пример расчета допусков для времени установления и удержания. Хост посылает импульс запуска преобразования на АЦП и считывает данные с его выхода.

tCYCLE = tJITTER + tSETUP + tPROP_DATA + tPROP_CLK + tDRV + tMARGIN,

где

tCYCLE: Тактовый период = 1/fCLOCK

tJITTER: Джиттер тактовых импульсов

tSETUP: Время установления хоста

tHOLD: Время удержания хоста

tPROP_DATA: Задержка распространения данных в линии передачи между АЦП и хостом

tPROP_CLK: Задержка распространения импульсов синхронизации в линии передачи между хостом и АЦП

tDRV: Время сохранения данных после переднего/заднего фронта тактового импульса

tMARGIN: Необходимый дополнительный запас времени. tMARGIN ≥ 0 означает, что требования по времени установления или удержания удовлетворяются, а в случае tMARGIN < 0 – не удовлетворяются.

|

|

| Рисунок 2. | Запасы по времени установления и удержания. |

Граница времени установления для хоста (tMARGIN_SETUP) определяется следующими составляющими:

tMARGIN_SETUP = tCYCLE, MIN – tJITTER – tSETUP – tPROP_DATA – tPROP_CLK – tDRV, MAX.

Выражение для времени установления определяет минимально допустимый период тактовой частоты как функцию максимальных системных задержек. Для соблюдения указанных в документации временных характеристик должно выполняться соотношение tMARGIN_SETUP ≥ 0. Если неравенство не выполняется, и необходимо компенсировать дополнительные системные задержки, увеличьте период (понизьте частоту) тактовых импульсов. Для буферов, трансляторов уровня, изоляторов и других вспомогательных компонентов на шине добавьте к tPROP_CLK и tPROP_DATA дополнительные задержки.

Аналогично, допуск на время удержания хоста равен

tMARGIN_HOLD = tPROP_DATA + tPROP_CLK + tDRV – tJITTER – tHOLD.

Формула для времени удержания tMARGIN_HOLD устанавливает требования к минимальной системной задержке, соблюдение которых позволит избежать возникновения логических ошибок. Согласно техническим спецификациям, это время не должно быть меньше нуля (tMARGIN_HOLD ≥ 0).

Многие АЦП последовательных приближений с интерфейсом SPI тактируют старший значащий бит спадающим фронтом CS или CNV, в то время, как остальные биты данных сдвигаются по заднему фронту SCLK, как это показано на Рисунке 3. При чтении старшего значащего бита вместо tDRV подставляйте в формулы «10».

|

|

| Рисунок 3. | Временные диаграммы сигналов на линиях интерфейса SPI микросхемы AD7980. (Трехпроводный режим). |

Таким образом, наивысшая скорость цифрового интерфейса зависит не только от максимальной частоты синхронизации, но еще и от времени установления, времени удержания, времени сохранения данных на выходе, задержки распространения и джиттера синхроимпульсов.

|

|

| Рисунок 4. | Цифровой интерфейс между ЦСП и микросхемой AD7980. |

На Рисунке 4 показано трехпроводное подключение управляющего процессора цифровой обработки сигналов (ЦСП), обращающегося к микросхеме AD7980, при напряжении питания интерфейса SPI VDRIVE = 3.3 В. ЦСП защелкивает сигнал SDO по спадающему фронту импульса SCLK. Указанные в документации на этот процессор минимальные времена установления и удержания равны 5 нс и 2 нс, соответственно. Время распространения по линиям печатной платы, изготовленной из типичного материала FR-4, составляет примерно 180 пс/дюйм. Задержка сигнала в буфере равна 5 нс. Общая задержка распространения для сигналов CNV, SCLK и SDO равна

tPROP = 180 пс/дюйм × (9" + 3") + 5 нс = 7 нс.

tJITTER = 1 нс.

Частота тактового сигнала, поступающего на вход SCLK от хоста, равна 30 МГц, следовательно, tCYCLE = 33 нс.

tMARGIN_SETUP = 33 нс − 1 нс – 5 нс – 7 нс – 11 нс – 7 нс = 2 нс.

tMARGIN_HOLD =11 нс + 7 нс + 7 нс – 1 нс – 2 нс = 22 нс.

Итак, допуски, как на время установления, так и на время удержания, положительны, что позволяет синхронизировать АЦП частотой 30 МГц.

Качество цифрового сигнала

Понятие целостности цифрового сигнала объединяет совокупность требований к параметрам временнóй диаграммы и собственно к качеству сигнала, и предполагает, что сигналы:

- доходят до приемника, сохраняя требуемые уровни напряжений,

- не влияют друг на друга,

- не нарушают работу других устройств,

- не засоряют электромагнитный спектр.

Качество сигнала определяется множеством составляющих, наиболее важные из которых показаны на Рисунке 5. В этом разделе мы остановимся на выбросах, звоне, отражениях и перекрестных помехах.

|

|

| Рисунок 5. | Параметры, определяющие характеристики целостности сигнала. |

Отражения являются следствием рассогласования импедансов. Импеданс изменяется на каждой неоднородности, через которые проходит сигнал на пути от передатчика к приемнику. Часть сигнала отражается обратно, а часть продолжает распространяться по линии. Отражения могут приводить к выбросам, провалам, звону и немонотонности фронтов тактовых импульсов на входе приемника.

|

|

| Рисунок 6. | Предельные эксплуатационные значения параметров микросхемы AD7606. |

Положительные и отрицательные выбросы напряжения могут разрушить цепь защиты входа или стать причиной сокращения срока службы микросхемы. На Рисунке 6 представлены взятые из технического описания значения предельных эксплуатационных параметров микросхемы AD7606. Напряжение на цифровых входах должно находиться в диапазоне от –0.3 В до VDRIVE + 0.3 В. Причиной неправильной работы логики могут также стать выбросы, при которых входное напряжение кратковременно может оказаться выше максимального или ниже минимального порогов переключения.

Для минимизации отражений:

- Делайте проводники по возможности короткими

- Контролируйте характеристический импеданс печатных проводников

- Избегайте разветвления дорожек

- Используйте соответствующие схемы согласования

- В качестве путей возврата тока используйте в отдельных слоях сплошные области металлизации с минимальными площадями петель

- Снижайте токи в сигнальных линиях и уменьшайте скорости их нарастания

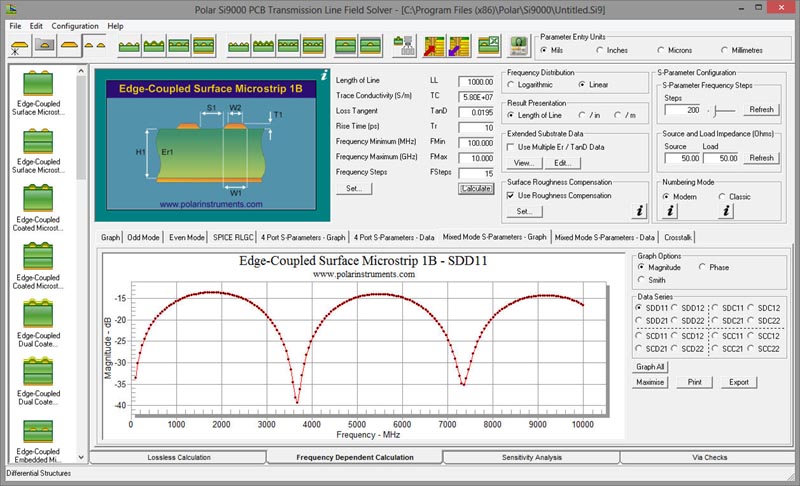

Для расчета характеристических импедансов проводников печатных плат разработано множество программных средств, таких, скажем, как анализатор полей Si9000 компании Polar Instruments (Рисунок 7). Подобные инструменты позволяют легко определить характеристический импеданс, выбрав модель передающей линии и указав такие параметры, как тип и толщина диэлектрика, ширина и толщина печатного проводника, а также его расположение относительно соседних дорожек.

|

|

| Рисунок 7. | Окно анализатора полей Si9000 компании Polar Instruments. |

IBIS является новым развивающимся стандартом описания поведения цифровых входов/выходов аналоговых микросхем. Analog Devices разработала IBIS-модели для всех АЦП последовательных приближений. Моделирование, предшествующее конструированию платы, позволяет проверить распределение сигналов синхронизации, выбрать типы корпусов, определить порядок чередования слоев, топологию цепей и стратегии согласования. Оно позволяет также сформулировать временные ограничения для сигналов последовательного интерфейса и выработать рекомендации по размещению элементов и трассировке печатной платы. Моделирование работы созданного устройства дает возможность проверить соблюдение всех требований и выявить источники таких нарушений, как отражения, звон и перекрестные помехи.

На Рисунке 8 показан драйвер, подключенный к входу SCLK1 с помощью 12-дюймовой (305 мм) микрополосковой линии, и второй драйвер, подключенный к выводу SCLK2, между выходом которого и микрополосковой линией добавлен последовательный резистор сопротивлением 43 Ом.

|

|

| Рисунок 8. | Передача импульсов SCLK в АЦП AD7606. |

На Рисунке 9 виден большой выброс на выводе SCLK1, выходящий за допустимые границы входного напряжения –0.3 В … +3.6 В. Последовательный резистор снижает скорость нарастания импульса на входе SCLK2, не позволяя сигналу выйти из зоны допустимых уровней.

|

|

| Рисунок 9. | Результаты IBIS-моделирования выбросов на входе синхронизации AD7606. |

Перекрестные помехи возникают между параллельными линиями передачи вследствие энергетических связей через взаимную емкость (электрическое поле) или взаимную индуктивность (магнитное поле). Уровень перекрестных помех зависит от времени нарастания сигналов, длины параллельных проводников печатной платы и расстояния между ними.

Вот несколько практических рекомендаций, соблюдение которых позволит взять перекрестные помехи под контроль:

- Увеличивайте расстояния между проводниками

- Минимизируйте длины параллельных путей сигнала

- Располагайте проводники ближе к слоям питания или «земли»

- Используйте соответствующие схемы согласования

- Ограничивайте скорости нарастания сигнала

Влияние цифровых узлов

При работе цифровых узлов характеристики АЦП последовательных приближений ухудшаются из-за снижения отношения сигнал/шум, обусловленного шумами шин цифровой земли и питания, джиттером импульсов выборки и помехами от цифровых сигналов.

Дрожание апертуры синхроимпульсов ограничивает отношение сигнал/шум, особенно для высокочастотных входных сигналов. Вклад в джиттер системы вносят два источника: апертурный джиттер расположенной на кристалле АЦП схемы выборки и хранения (внутренний джиттер) и джиттер импульсов выборки (внешний джиттер). Апертурный джиттер возникает вследствие разброса времени выборки от преобразования к преобразованию и зависит только от характеристик АЦП. Джиттер импульсов выборки обычно является доминирующим источником ошибок, но как внутренний, так и внешний источники проявляют себя одинаково, вызывая отклонения времен выборки аналогового входа, что проиллюстрировано Рисунком 10. Внешне оба эффекта неразличимы.

|

|

| Рисунок 10. | Напряжение ошибки, обусловленное джиттером импульсов выборки. |

Общий джиттер является источником напряжения ошибки, ограничивающего полное отношение сигнал/шум (SNR) АЦП значением

где

f – частота сигнала на аналоговом входе,

tJ – общий джиттер системы (с.к.з.).

Общий джиттер равен

где

tA – апертурный джиттер АЦП,

tS – джиттер импульсов выборки.

Так, например, при частоте сигнала на аналоговом входе 10 кГц и общем джиттере 1 нс предельное значение отношения сигнал/шум равно 84 дБ.

Шумы источника питания, создаваемые цифровыми выходами при их переключении, должны быть изолированы от чувствительных источников питания аналоговых цепей. Питание аналоговых и цифровых узлов необходимо разделять, обращая особое внимание на общие пути возврата тока.

На высокоточные АЦП последовательных приближений может оказывать влияние работа цифрового интерфейса, даже при правильной развязке и изоляции источника питания. Хорошие результаты может давать периодическое отключение синхронизации. В справочных данных, как правило, указываются интервалы времени, когда цифровой интерфейс может находиться в неактивном состоянии. Однако минимизация времени работы цифровых блоков, заключающаяся, как правило, в их отключении на период выборки и в конце преобразования во время определения младших битов результата, на высоких скоростях может оказаться непростой задачей.

Заключение

Чтобы получать от АЦП последовательных приближений правильные результаты преобразований, обращайте особое внимание на работу цифровых узлов, помехи от которых могут установить АЦП в неопределенное состояние, приводить к сбоям в работе или ухудшать его характеристики. Эта статья должна помочь разработчикам в поиске первопричин некорректной работы АЦП и нахождении способов их устранения.

Ссылки

- Application Note AN-932, Power Supply Sequencing.

- Kester, Walt. “Data Converter Support Circuits.” Data Conversion Handbook, Chapter 7. Analog Devices, Inc., 2004.

- Brannon, Brad. AN-756 Application Note. Sampled Systems and the Effects of Clock Phase Noise and Jitter. Analog Devices, Inc., 2004.

- Ritchey, Lee W. Right the First Time: A Practical Handbook on High-Speed PCB and System Design, Volume 1. Speeding Edge, 2003.

- Usach, Miguel. AN-1248 Application Note. SPI Interface. Analog Devices, Inc., 2013.

- Casamayor, Mercedes. AN-715 Application Note. A First Approach to IBIS Models: What They Are and How They Are Generated. Analog Devices, Inc., 2004.

Купить AD7606 на РадиоЛоцман.Цены

Купить AD7606 на РадиоЛоцман.Цены