Christoph Hammerschmidt

Компания Renesas включила в архитектуру микропроцессора V850 сопроцессор цифровой обработки данных DSP, что позволяет ему занять равные позиции с доступными специализированными процессорами DSP. Такой подход добавления сопроцессора в микросхему дает массу преимуществ.

Renesas планирует в дальнейшем развивать эту архитектуру для того, чтобы удовлетворять требованиям мощных вычислительных приложений для реального времени, таких как автоматизация промышленного производства и системы управления двигателем в автомобилях.

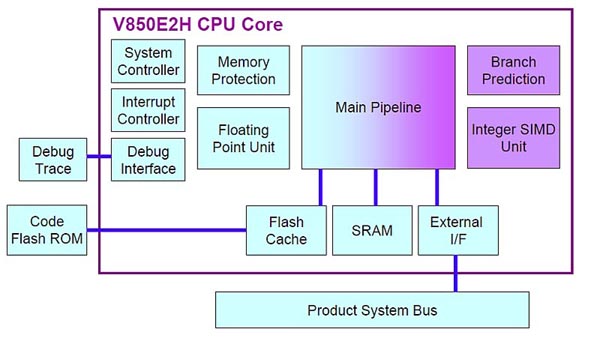

Проектировщики компании Renesas, добавив сопроцессор, обеспечили возможность микропроцессору за время выполнения одной инструкции (команды) обработать до четырех элементов данных (принцип параллельных вычислений SIMD). Помимо 64-битных регистров SIMD, сопроцессор оснащен специальным конвейером для обработки расширенного набора команд.

Дополнительно в новой архитектуре имеется высокоскоростной предиктор, позволяющий оптимизировать циклы исполняемых команд. Его наличие позволяет примерно на 10 процентов увеличить производительность микропроцессора, даже при исполнении программ, не связанных с обработкой сигналов.

Эти две особенности являются основными новшествами для разрабатываемых компанией Renesas микропроцессоров V850E2v4. Первое ядро, основанное на этой архитектуре, получило название V850E2H.

Эта архитектура не только ускоряет выполнение готовых программ, но и сокращает процесс их разработки и отладки. Поскольку здесь нет необходимости во внешнем DSP процессоре, управляющая программа и программа DSP разрабатываются и тестируются в одной среде разработки, в отличие от ранее использовавшихся методов, когда эти элементы разрабатывались раздельно. Этап окончательной интеграции и тестирования управляющей программы и программы DSP в новой архитектуре не нужен.

В приложениях, где проявляются достоинства нового сопроцессора, размер программного кода может быть значительно сокращен с одновременным впечатляющим увеличением производительности.

Компания Renesas описывает 16 битовый алгоритм быстрого преобразования Фурье по 128 точкам для новой архитектуры в сравнении с этой же процедурой, написанной на языке С для микропроцессора с предыдущий архитектурой. Компания заявляет, что при сокращении программного кода на одну треть, скорость выполнения программы на новой архитектуре увеличилась в 12 раз.

Одновременно ядро процессора V850E2H обеспечивает совместимость в пределах базового набора команд на объектном уровне с более ранним ядром процессора V850E2M. Совместимое устройство для обработки арифметических операций с плавающей точкой IEEE 754, которое использовалось вместе с процессором V850E2M, может также использоваться и с новым ядром V850E2H.

Компания Renesas уверена в том, что отличные свойства процессора V850E2H для обработки сигналов и управления технологическими процессами, позволят ему обеспечить существенный вклад в развитие программ для систем управления, требующих сложных алгоритмов анализа, таких как системы гашения вибраций на промышленном оборудовании или системы бортового контроля в автомобилях (обработка сигналов датчиков сближения, в системах эффективного приготовления топливной смеси для двигателя).

Компания Renesas планирует предложить клиентам новые решения с использованием нового ядра микропроцессора V850E2H.

Данных о цене и наличии нового ядра микропроцессора V850E2H не приводится.