Журнал РАДИОЛОЦМАН, январь 2015

Михаил Русских

Описываются микроконтроллеры серии PIC16F170x/171x, поясняется принцип работы конфигурируемой логической ячейки, модуля мультиплексирования периферии и генератора комплементарных импульсов.

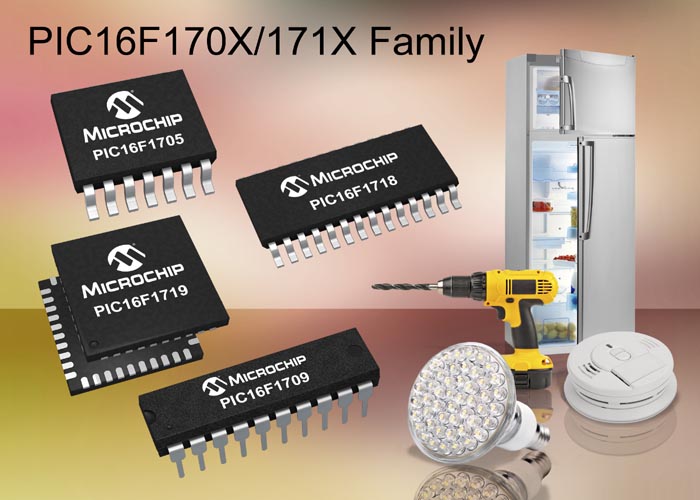

Весной 2014 года компания Microchip выпустила семейство 8-разрядных микроконтроллеров PIC16F170x/171x. Ключевой особенностью, отличающих их от других устройств этого класса, стало наличие независимой от ядра интеллектуальной периферии, которая существенно расширяет возможности новых микроконтроллеров, делая их надежным решением для создания бытовых приборов, зарядных устройств, электроинструментов и устройств управления светодиодным освещением.

Имеющиеся в составе PIC16F170x/171x конфигурируемые логические ячейки позволяют реализовать достаточно сложные логические функции, не занимая ресурсы ядра. Генератор комплементарных импульсов, также присутствующий в данных микроконтроллерах, полезен при построении мостовых или полумостовых схем, поскольку может создавать комплементарные сигналы с заранее запрограммированными задержками, чтобы безопасно управлять ключами. Это позволяет сэкономить на элементах, сократив внешнюю обвязку мостовых схем.

Приборы серии PIC16F170x/171x первыми среди устройств PIC16 получили технологию Peripheral Pin Select, позволяющую связывать входы и выходы периферийных модулей с различными выводами микроконтроллера. Помимо этого PIC16F170x/171x имеют в своем составе программируемый высокоточный линейный генератор частоты (NCO), два операционных усилителя и модуль детектирования перехода сигнала через ноль.

В этом материале будет приведена основная информация об особенностях данных микроконтроллеров, что позволит сориентировать разработчиков встраиваемых систем при принятии решения об использовании этих устройств в своих проектах.

Модуль мультиплексирования периферии

Благодаря модулю мультиплексирования периферии (Peripheral Pin Select), программист может самостоятельно выбирать входные и выходные цифровые выводы для определенного периферийного блока. Для каждого периферийного блока задается линия ввода/вывода, которая будет являться для него входом. При этом несколько периферийных модулей в качестве источника сигнала могут иметь один и тот же вывод. Также каждой линии ввода/вывода можно поставить в соответствие выход того или иного периферийного модуля.

Если необходимо организовать двунаправленные линии передачи данных, например, для модуля EUSART и модуля MSSP, работающего в режиме шины I2C, то в таком случае вход периферийного блока должен указывать на тот же вывод, который выбран в качестве выхода для данного блока.

Кроме того, для предотвращения случайных изменений в назначении выводов, саму возможность переназначения можно заблокировать. В ходе выполнения программы, при желании, можно осуществить разблокировку, что позволит вновь менять назначение выводов. Также можно заблокировать возможность переназначения до следующего сброса микроконтроллера. После этого во время работы микроконтроллера статус линий ввода/вывода изменить будет невозможно.

Конфигурируемая логическая ячейка

Микроконтроллеры PIC16F170x/171x могут иметь в своем составе до четырех конфигурируемых логических ячеек, которые предоставляют разработчику возможность запрограммировать логическую функцию, независящую от работы ядра.

|

|

| Рисунок 1. | Блок выборки входных данных и логические вентильные группы; биты LCxDxG1T разрешают прохождение сигнала через вентили. |

На вход логической ячейки может быть подано до 32 сигналов. Ими могут быть сигналы с линий ввода/вывода, периферийных модулей, импульсы внутренней тактовой частоты, а также биты регистров. Сначала эти сигналы поступают на четыре мультиплексора блока выборки входных данных (Рисунок 1). Выход каждого мультиплексора представлен инвертированным и неинвертированным сигналами, которые поступают на четыре логические вентильные группы. На входе каждой вентильной группы может быть до четырех сигналов, над которыми можно произвести одну из базовых логических операций («И», «И-НЕ», «ИЛИ» и «ИЛИ-НЕ»).

На вход также может не поступать ни одного сигнала, тогда состояние на выходе вентильной группы (логический «0» или логическая «1») задается программистом. Сигналы с выходов вентильных групп заводятся на входы логической функции, с помощью которой можно реализовать следующие элементы: И-ИЛИ, ИЛИ-исключающее ИЛИ, И, RS-триггер, D-триггер с выводами Set и Reset, D-триггер с выводом Reset, JK-триггер с выводом Reset, регистр с выводами Set и Reset. На Рисунке 2 показаны все эти элементы.

|

|

| Рисунок 2. | Варианты логических функций, доступных для реализации. |

С выхода логической функции сигнал поступает на вентиль, который разрешает его дальнейшее прохождение к входу элемента, позволяющего инвертировать этот сигнал. Выход логической ячейки можно настроить на генерацию прерываний. При этом прерывание можно организовать как по фронту, так и по спаду сигнала.

Поскольку конфигурируемая логическая ячейка работает независимо от ядра, она может функционировать и в режиме сна. При этом если в качестве входного сигнала был выбран системный источник тактовых импульсов, то вместо него к входу будет подключен высокочастотный внутренний генератор HFINTOSC. Разработчику следует учитывать, что при работе логической ячейки энергопотребление микроконтроллера в режиме сна увеличивается.

Генератор комплементарных импульсов

Основной функцией этого генератора является преобразование одиночного ШИМ-сигнала в два комплементарных ШИМ-сигнала. Также на основе двух независимых входных событий он может формировать один или два комплементарных ШИМ-сигнала.

Частота полученного сигнала ШИМ определяется временным промежутком между фронтами одного или двух входных сигналов, а период – промежутком между фронтом и спадом сигнала или сигналов. Источники, фронт или спад которых являются определяющими, назначаются программистом. В качестве таких источников могут выступать линии, выбранные в регистре модуля мультиплексирования для данного периферийного блока, выход первого компаратора (C1OUT), выход второго компаратора (C2OUT), выход первой конфигурируемой логической ячейки (CLC1), выход первого модуля захвата/сравнения (CCP1), выход второго модуля захвата/сравнения (CCP2) и выход третьего модуля ШИМ (PWM3). Входное событие, вызванное этими источниками, может регистрироваться как по уровню, так и по границе сигнала. В первом случае входной сигнал регистрируется после некоторой задержки, позволяющей ему дорасти до необходимого уровня, соответствующего логической «1» или упасть до уровня логического «0». Во втором случае входное событие будет детектировано сразу же после того, как будет зафиксировано нарастание или спад. На практике периодические сигналы желательно регистрировать по границе, а непериодические сигналы порогового напряжения – по уровню.

Для формирования задержек генератор комплементарных импульсов имеет вход тактирования. При этом в качестве тактирующей частоты может выступать частота внутреннего генератора HFINTOSC, способного работать в спящем режиме, системная частота ядра (Fosc) или частота тактирования инструкций (Fosc/4).

Генератор комлементарных импульсов имеет четыре выхода: COGxA, COGxB, COGxC и COGxD. Эти выходы можно настроить либо на вывод сигналов генератора, либо на выдачу статического сигнала. При этом уровень статического сигнала по выбору программиста может соответствовать как логическому «0», так и логической «1».

Генератор комлементарных импульсов характеризуется несколькими режимами работы. К самому простому можно отнести режим непосредственной выдачи ШИМ-сигнала. В этом случае ШИМ-сигнал входного источника может быть доступен на любом выходе генератора. Также можно организовать режим синхронной выдачи ШИМ-сигнала. Он отличается от предыдущего только тем, что сигнал на выходе формируется лишь после появления фронта сигнала источника, а не сразу после активации режима выдачи ШИМ-сигнала, как в первом случае.

Ко второй категории режимов относятся прямой и реверсивный полномостовые режимы. При выборе этих режимов два из четырех выходов будут активными, оставшиеся два – неактивными. Один из активных выходов модулируется входным ШИМ-сигналом, другой имеет полностью заполненный период, то есть его сигнал постоянно находится в высоком логическом уровне. При прямом включении полного моста модулируемым является выход COGxD, а период сигнала на выходе COGA заполняется полностью. В реверсивном режиме модулируется сигнал выхода COGxB, в то время как на выходе COGxC присутствует сигнал высокого логического уровня. При изменении направления, то есть при переходе из прямого режима в реверсивный, или наоборот, организуется задержка, называемая «мертвым» временем, благодаря которой включение одного из выходов происходит немного позже отключения другого выхода того же плеча мостовой схемы. Это позволяет избежать появления тока короткого замыкания. Пример перехода из прямого режима в реверсивный показан на Рисунке 3.

|

|

| Рисунок 3. | Переход из прямого режима в реверсивный. |

Также функционирование генератора комплементарных импульсов возможно в режиме полумоста. В этом случае сигналы двух выходов (COGxA и COGxB или COGxC и COGxD) будут комплементарны друг относительно друга. Благодаря организации задержек по фазе и «мертвого» времени, можно сделать так, чтобы один сигнал отличался от другого не только за счет инвертированной фазы. Наглядно это можно продемонстрировать на Рисунке 4.

|

|

| Рисунок 4. | Изменение формы сигнала в полумостовом режиме; а – период «мертвого» времени после события с определяющим спадом, б – задержка по фазе, в – период «мертвого» времени после события с определяющим фронтом. |

Последним режимом работы генератора комплементарных импульсов является двухтактный режим, когда два выхода (COGxA и COGxB или COGxC и COGxD) формируют сигналы, период которых в два раз больше периода входного ШИМ-сигнала. При этом выходные сигналы смещены друг относительно друга на один период ШИМ-сигнала. На Рисунке 5 проиллюстрирован принцип работы генератора в этом режиме.

|

|

| Рисунок 5. | Двухтактный режим работы. |

Как уже упоминалось ранее, генератор комплементарных импульсов для предотвращения возникновения токов короткого замыкания и для реализации требуемой формы выходного импульса может формировать периоды «мертвого» времени. Для этого он имеет в своем составе два таймера, один из которых используется для формирования задержки по фронту, другой для формирования задержки по спаду. Каждый таймер может работать в режиме асинхронного каскада задержки или синхронного счетчика.

В режиме асинхронного каскада задержка определяется временем, за которое входной сигнал проходит через ряд элементов этого каскада. Время прохождения каждого элемента составляет 5 нс. Количество элементов, участвующих в формировании каскада задержки, указывается программистом. В режиме синхронного счетчика «мертвое» время определяется периодом работы таймера COG_clock, который ведет счет от нуля до значения, также определяемого программистом.

Кроме «мертвого» времени можно организовать бланкирующую задержку, во время которой входной сигнал может быть «погашен» (бланкирован) на короткий промежуток времени. Это позволяет предотвратить возникновение нежелательных переходных процессов, вызванных включением или выключением силового оборудования при подаче ложных входных сигналов.

Генератор комплементарных импульсов имеет два счетчика бланкирующей задержки. Первый бланкирует входные события с определяющим нарастанием сигнала. При этом счет начинается по событию с определяющим спадом сигнала. Отсчет ведется таймером COG_clock, начиная с нуля и заканчивая установленным программистом значением. Второй счетчик, наоборот, бланкирует входные события с определяющим спадом сигнала, а счет начинается по событию с определяющим нарастанием сигнала.

Помимо «мертвого» времени и бланкирующей задержки можно организовать задержку по фазе. То есть, можно отсрочить действие события как с определяющим нарастанием, так и с определяющим спадом сигнала. На Рисунке 4 можно наблюдать пример использования задержки по фазе.

Генератор комплементарных импульсов может изменять состояния выходов таким образом, чтобы обеспечить безопасное автоматическое отключение цепи. Отключение может быть произведено как программно, так и по внешнему входному сигналу. При отключенном автоматическом перезапуске выходы будут находиться в отключенном состоянии до первого события с определяющим нарастанием сигнала, если до этого бит активации режима автоматического отключения был сброшен программно. При включенном автоматическом перезапуске данный бит будет сброшен автоматически. Тогда выходы генератора комплементарных импульсов будут работать в нормальном режиме после появления события с определяющим фронтом сигнала, если при этом состояние входного сигнала, инициирующего отключение, будет находиться в низком логическом уровне.

Отключение по внешнему входному сигналу обеспечивает более быстрый способ перевода выходов генератора в нерабочий режим при возникновении внештатной ситуации. В качестве источника внешнего сигнала можно указать выход первого компаратора (C1OUT), выход второго компаратора (C2OUT), выход второй конфигурируемой логической ячейки (CLC2OUT), а также любую линию, выбираемую в регистре мультиплексирования периферии. В качестве источников могут одновременно выступать несколько выбранных сигналов, или даже все.

При автоматическом отключении выходы генератора комплементарных импульсов могут быть переведены в одно из четырех состояний: состояние высокого логического уровня, состояние низкого логического уровня, высокоимпедансное состояние, неактивное состояние ШИМ (такое же состояние, которое вызывается событием с определяющим спадом сигнала).

Генератор комплементарных импульсов также может функционировать во время пребывания микроконтроллера в режиме сна. При этом в качестве источника тактовых импульсов COG_clock выбирается внутренний генератор HFINTSOC.