PCI – фактически стандартная шина, ставшая локальной шиной для микрокомпьютерных систем и все персональные компьютеры имеют шину PCI в своем составе. Однако, хотя эта шина так распространена, кажется невозможным эксперимент, в котором бы она использовалась. PCI кажется такой, что руки любителя никогда ее не коснутся, несмотря на ее высокую производительность.

Фактически невозможно создать PCI плату, которая бы удовлетворяла требованиям стандарта PCI, из одних только стандартных логических микросхем. Но PCI сложная как целая система, однако ее основная часть работают по очень простому протоколу. Поэтому, вполне возможно, чтобы PCI-плата, работающая только как ведомое устройство, была выполнена на небольшой микросхеме программируемой логики. Но следует заметить, что PCI-плата собранная подобным образом не является полноценным PCI устройством и не должна использоваться для управления чем либо. Это лишь эксперимент, производимый с целью понять работу шины PCI.

Основные циклы шины

Цикл записи

Это простейший цикл шины. Устройство назначения определяет начало цикла шины по установившемуся сигналу FRAME#, при следующем тактовом цикле. Как только цикл шины инициирован, команда и адрес выдаются всем устройствам, подключенным к шине, и устройство, определившее, что этот цикл для него, устанавливает сигнал DEVSEL#, отвечая таким образом шине. Поскольку устройство назначения отвечает за 1 такт, это называется быстрое декодирование. Если бы устройство назначения ответило бы на второй или третий цикл тактовой частоты, это было бы среднескоростным или медленным декодированием.

После того, как устройство назначения ответит сигналом DEVSEL#, оно удостоверяется в том, что сигнал IRDY# установлен (записываемые данные верны), и берет данные. В то же самое время устройство назначения знает, что это последний цикл передачи, поскольку FRAME# не установлен, а IRDY# установлен, что означает, текущие данные – последние.

Когда последние данные взяты, устройство назначения сбрасывает сигналы DEVSEL# и TRDY#, эти сигналы будут освобождены при следующем тактовом цикле, таким образом устройство назначение завершило цикл шины.

.png)

Цикл чтения

Это простейший цикл чтения. Здесь требуется один такт буферного цикла, так как агент, который управляет линиями адреса/данных меняется. Таким образом цикл чтения по сравнению с циклом записи требует на один такт больше.

Устройство назначения определяет начало цикла по установившемуся сигналу FRAME# при втором тактовом сигнале (см. рисунок). Как только цикл шины инициирован, команда и адрес выдаются всем устройствам шины. Устройство, которое определило, что этот цикл для него, устанавливает сигнал DEVSEL#, что бы ответить на цикл шины. В этом случае, потому как устройство отвечает на второй цикл, это среднескоростное декодирование. Необходимо выставить данные на шину с паузой в 1 такт, чтобы сменить агента, управляющего линиями адреса/данных. Для этого все равно потребуется 1 такт, даже если устройство ответит в режиме высокоскоростного декодирования.

После двух циклов тактовой частоты с момента старта цикла шины, устройство назначения помещает данные на линии адреса/данных и устанавливает сигнал TRDY#. При следующем тактовом цикле, устройство назначения проверяет сигнал IRDY#. Если IRDY# установлен (инициатор принял данные), передача данных завершена. Сигнал FRAME# сброшен, это значит, что текущие данные последние. Устройство назначения обнаруживает это и завершает транзакцию.

После того, как последние данные переданы, устройство назначения сбрасывает сигналы DEVSEL# и TRDY#, эти сигналы будут освобождены при следующем тактовом цикле, транзакция на этом заканчивается.

.png)

Цикл записи (Передача Очередью)

Передача очередью не отличается от отдельной передачи. Устройство назначения проверяет сигнал FRAME# при каждой передаче данных. Если сигнал FRAME# остается установленным, устройство назначения распознает это как следующую передачу данных. Так работает передача очередью. Передача очередью в основном применяется для доступа к памяти, однако может использоваться и для доступа к устройствам ввода/вывода.

Передача очередью демонстрирует наибольшую производительность PCI. Это легко представить, если вспомнить, что в шине PCI адрес и данные мультиплексированы. При передаче очередью адрес назначения определяется 1 раз при старте передачи данных, и этого вполне достаточно. Таким образом PCI уменьшает число проводов, стоимость, но также и стабильность передачи данных.

.png)

Быстрая компенсационная транзакция

Метод первой компенсационной транзакции определен для того, чтобы сделать использование шины эффективным.

Обычно, по крайней мере один тактовый цикл ожидания существует между двумя циклами шины (транзакции). Цикл ожидания это буферное время, чтобы предотвратить коллизии. Однако от этого можно отказаться, когда переключения устройств не происходит между циклами шины.

.png)

Работа платы ввода/вывода: Состояния

Поскольку PCI полностью синхронная шина, все операции основаны на системной частоте. В PCI пате необходимо реализовать, концепцию конечного автомата, при которой команда от инициатора обязательно должна быть выполнена. Наша плата ввода вывода реализует конечный автомат всего на одной плис (GAL22V10). Теперь давайте перечислим состояния и связи, представим их на рисунке и объясним.

.png)

СОСТОЯНИЕ 4

Шина в ожидании. Начало нового цикла шины определяется из этого состояния. Из этого состояния устройство может перейти в СОСТОЯНИЕ 2 или СОСТОЯНИЕ 3, когда цикл ввода/вывода инициируется для данного устройства. Также возможен переход в СОСТОЯНИЕ 0, когда запускается цикл шины, не взаимодействующий с этим устройством.

СОСТОЯНИЕ 0

Шина не с в состоянии ожидания. Выполняется любая другая транзакция. Ожидаем, пока шина перейдет в состояние ожидания. Из этого состояния не может начинаться новый цикл.

СОСТОЯНИЕ 2

Цикл записи для этого устройства запущен. Устройство устанавливает сигнал DEVSEL# и отвечает циклу шины. В тоже время, устройство устанавливает сигнал TRDY# и показывает, что данные для записи приняты. В тоже самое время устройство защелкивает данные и переходит в СОСТОЯНИЕ 3, когда сигнал IRDY# установлен (инициатор может принять прочитанные данные) и сигнал FRAME# не установлен (последние данные).

СОСТОЯНИЕ 3

DEVSEL# и TRDY# не установлены. Обычно, DEVSEL# и TRDY# освободятся при следующем цикле тактовой частоты, устройство переходит в ожидание (СОСТОЯНИЕ 0). Но, оно непосредственно переходит в СОСТОЯНИЕ 2 или СОСТОЯНИЕ 5 без прохождения через состояние ожидания (быстрая компенсационная транзакция).

СОСТОЯНИЕ 5

Старт цикла чтения. DEVSEL# и TRDY# не установлены. Обычно, DEVSEL# и TRDY# освободятся при следующем цикле тактовой частоты, устройство переходит в ожидание (СОСТОЯНИЕ 0). Но, оно непосредственно переходит в СОСТОЯНИЕ 2 или СОСТОЯНИЕ 5 без прохождения через состояние ожидания (быстрая компенсационная транзакция).

СОСТОЯНИЕ 6

Цикл чтения в процессе. Устройство назначения устанавливает сигнал DEVSEL# и отвечает на цикл чтения. В тоже время на линии адреса/данных выставляются считываемые данные и устанавливается сигнал TRDY#. В тоже время устройство переходит в СОСТОЯНИЕ 7, когда IRDY# установлен (инициатор может принять данные) и сигнал FRAME# не установлен (последние данные).

СОСТОЯНИЕ 7

Цикл чтения закончен. Устройство назначения сбрасывает сигналы DEVSEL# и TRDY#. Тогда сигналы DEVSEL# и TRDY# освобождаются при следующем такте и шина переходит в ожидание.

СОСТОЯНИЕ 1

Это состояние не определено. Даже если устройство перейдет в него в результате ошибки, оно сразу же перейдет в СОСТОЯНИЕ 0 при следующем цикле тактовой частоты, и возвращается в нормальный цикл.

Нарушения правил разработки

Схема устройства в этом эксперименте упрощена путем частичного исключения функций, необходимых для стандарта PCI. Я поясню исключенные функции и вред от их исключения. Это никогда не станет причиной проблем.

Отсутствие регистра конфигурации

Система определяет существование в системе PCI устройства используя регистр конфигурации. Он реализован в устройстве для установки функции устройства как PCI устройства или для перемещения адресов ресурсов чтобы избежать конфликтов.

Адрес назначения в этом устройстве декодируется фиксировано, без подключения регистра конфигурации. Вы должны установить адрес назначения так, чтобы не возникало конфликтов ресурсов, поскольку существование устройства не распознается системой. Наша PCI плата будет смеятьсяJ

Отсутствует функция генерации и проверки четности

Ошибка четности обязательно произойдет при цикле чтения, поскольку проверка или управление сигналом четности не выполняется. Любая операция, такая как NMI произойдет, когда обнаружится ошибка четности, если бит, отвечающий за ошибку четности в конфигурационном регистре инициатора (PCI контроллер) установлен. Но всего этого не произойдет, так как этот бит в персональных компьютерах обычно сброшен.

Старшие 16 бит адреса не распознаются

Только младшие 16 бит адреса декодируются нашей платой, хотя PCI устройство должно декодировать все 32 бита адреса. Но это не вызывает проблем, поскольку запросы к пространству адресов выше 64 килобайт в персональных компьютерах не происходят.

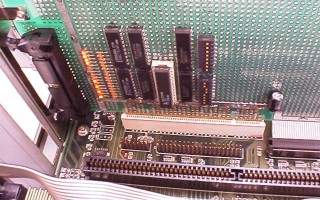

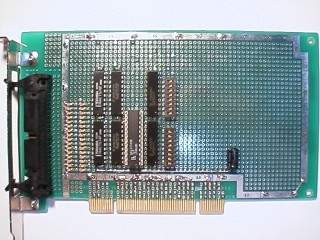

Сборка PCI платы

Я использую макетную плату для PCI MCC-331(Sunhayato). Она имеет монтажный разъем, поэтому легче в использовании.

ПЛИС должна быть в диапазоне быстродействия 7 нс или быстрее. Даже 7 нс спецификации PCI. Но так как приобрести ПЛИС с быстродействием выше 5 нс проблематично, ПЛИС используется на границе своих возможностей. Это не вызывает проблем.

Все другие детали типовые и выбирать их производителя не требуется. Ввод и вывод имеют разрядность 16 бит, поскольку это отнимает свободное место на разъеме, хотя существуют применения, где требуются все 32 бита.

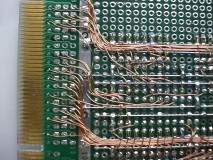

Поскольку это цифровая схема, я думаю долго возиться с ней не придется. Так как на ней много проводов, полезно будет посмотреть это для правильной прокладки проводов. Не используйте любые другие провода, так как в этом случае это становится похожим на гору. Вы должны очень тщательно прокладывать провода, ошибки недопустимы. Здесь легко ошибиться. Я тоже ошибаюсь иногда J. В особенности опасна ошибка подключения контактов разъема, по которым подается питание, это может вывести из строя материнскую плату. Более того, вы должны усилить питающую линию полностью, потому как она работает на высоких частотах, с максимумом в 33 МГц.

Тест и Результат

Во первых, установите адрес ввода/вывода для этого устройства с помощью переключателей на плате. Поскольку младшие 2 бита не декодируются, 4 байта, которые они составляют занимаются этим устройством. Шина будет конфликтовать когда адрес ввода/вывода дублируется с любым другим устройством PCI в одно и тоже время. Ненужно говорить, что вы должны выбрать адрес, который никем не используется.

Например, когда в устройстве установлен адрес F300h, оно отвечает на адреса с F300h по F303h.

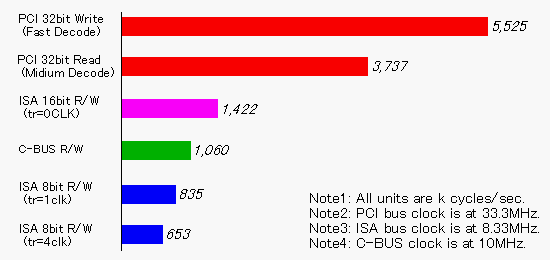

Сравним производительность. Тест считает количество циклов в секунду, которые взаимодействуют с устройством. Вот результаты:

Как и следовало ожидать PCI показал огромную производительность по сравнению с ISA. Для операции записи 6 тактов/цикл, чтения – 9 тактов/цикл как показали вычисления. Но, так как теоретически на запись/чтение требуется 3 и 4 такта соответственно, мы можем утверждать, что скорость передачи не достигает своего максимума (слишком большое время ожидания на шине). Потеря времени по всей видимости происходит на контроллере PCI материнской платы. Однако, PCI разработана так, что наилучшая производительность достигается при передаче очередью. Снижение производительности при отдельной передаче неизбежно.

Так же имеются различия в скорости передачи, почти в два раза на шине ISA, при 8ми и 16 битном доступе. Здесь цикл уменьшается, когда устройство отвечает как 16 битное. Это хорошо, когда даже 8 битное устройство может работать с -IOCS16, когда имеется возможность повысить производительность шины ISA.

Замечания

Ну и как вам статья? Шина PCI, которая казался столь сложной и не возможной для изучения, так же может использоваться и для любительских целей. Хотя все же в общем она кажется сложной, можно заметить, что она основана на удивительно простых процессах.