Сдвиговый регистр и несколько микросхем стандартной логики позволяют выделить сигнал синхронизации из потока данных.

При последовательной передаче, поток данных содержит в своем составе сигнал синхронизации, и, поэтому, сигнал синхронизации можно выделить на приемном конце. В этой Дизайн-идее описывается алгоритм восстановления данных/сигнала синхронизации для 1.5-МБитного потока данных Без-Возврата-к-Нулю (NRZ) микросхемах FPGA семейства Spartan XC3S200 компании Xilinx.

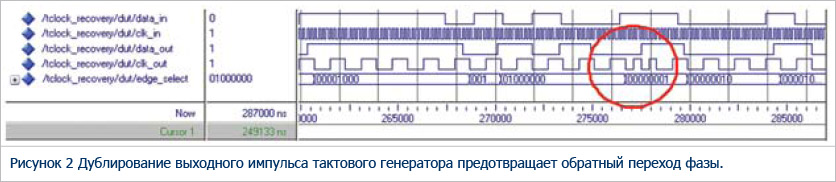

Алгоритм использует модифицированный алгоритм восстановления данных, описанный в рекомендациях по применению (application note) компании Xilinx. В рекомендациях по применению используется бок формирования тактового сигнала (DCM) моделей микросхем семейств Spartan или Virtex компании Xilinx, но эти приложения используют упрощенный алгоритм, который сравнивает фронты импульсов данных, если они присутствуют, с фронтами импульсов внутреннего тактового генератора, динамически изменяя задержку между входными данными и выходными данными. Простейший алгоритм пригоден для интеграции его в маленькие микросхемы CPLD или FPGA, в которых отсутствует DCM (рис.1).

Алгоритм использует 3-разрядный автономный счетчик для генерации выходного тактового сигнала, 8-разрядный сдвиговый регистр под выборки данных, семь элементов XOR для обнаружения фронтов импульсов, мультиплексор 7-в-1 с декодером для мультиплексирования бит, сдвигаемых вправо регистром, на выход схемы, и некоторого количества буферных регистров. Алгоритм должен работать в восемь раз быстрее, чем скорость последовательного потока данных, при неизвестных фазовых соотношений между обоими. При этом с каждым импульсом тактовой частоты в регистр будут записываться данные, таким образом, что после восьми циклов тактовой частоты, сдвиговый регистр будет содержать нарастающий фронт, спадающий фронт или, если входные данные остались без изменения, совсем не будет содержать фронта импульсов. Мультиплексор не обрабатывает случаи, при которых сдвиговый регистр не содержит фронтов, или содержит более одного фронта.

Местонахождение фронта в сдвиговом регистре определяется с помощью массива логических элементов Исключающее ИЛИ (XOR), который сравнивает бит 0 сдвигового регистра с битом 1, бит 1 с битом 2 итак далее. В зависимости от состояния массива логических элементов Исключающее ИЛИ (XOR), указывающего на место расположения фронта, некоторое количество битов сдвигового регистра передаются на выход. Эти действия приводят к тому, что выходной тактовый сигнал всегда переключается примерно в середине бита выходных данных.

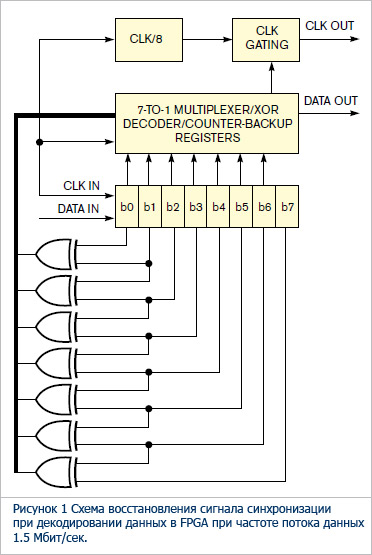

При небольшом рассогласовании в частоте тактового сигнала и входных данных - например, в случае возникновения фазового шума или отклонения частоты тактового генератора от номинального значения – фаза входных данных непрерывно подстраивается в соответствии с фазой выходного тактового сигнала, поскольку алгоритм отслеживает фазу входного сигнала. В этом случае, мультиплексор оказывается в состоянии переполнения, которое наступает, когда бит 7 сдвигового регистра мультиплексируется на выход схемы, следующим битом будет бит 1 сдвигового регистра, или наоборот.

Если на выходе первым появляется бит 7 – то есть фронт сигнала записывается как состояние 0100 0000 – и следующим выбранным битом будет бит 1 – то есть фронт сигнала записывается как состояние 0000 0001, то происходит переход фазы в выходных данных. Этот переход фазы составляет -360°×7/8, или -315°. Поскольку следующий бит данных уже полностью загружен в сдвиговый регистр, необходимо сформировать дублирующий выходной тактовый импульс с тем, чтобы регистр не потерял бит данных (обведенная область на рис.2).

Если на выходе первым появляется бит 1, с фронтом сигнала 0000 0001, и мультиплексор переходит к биту 7, с фронтом сигнала 0100 0000, то переход фазы в выходных данных составляет 360°×7/8 или 315°. Поскольку 7-й бит данных сдвигового регистра является задержанным вариантом последнего засинхронизированного бита, b1, выходной тактовый сигнал необходимо остановить на один период. Иначе, иначе один бит дважды пройдет на выход схемы (обведенная область на рис.3).

Для решения задачи переполнения переходов фазы в выходном тактовом сигнале можно использовать стандартные схемы комбинационной логики.